Using CCS 6.0.1.00040 and tirtos 2.0.2.36 with included tivaware on the Tiva C 123G launchpad.

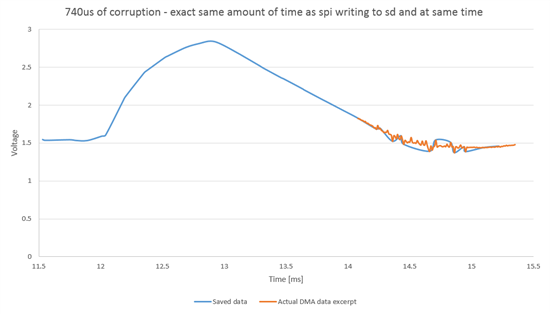

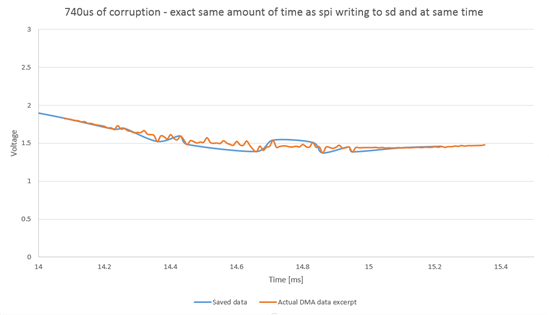

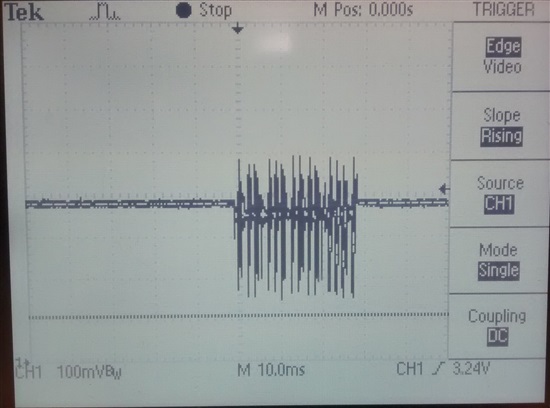

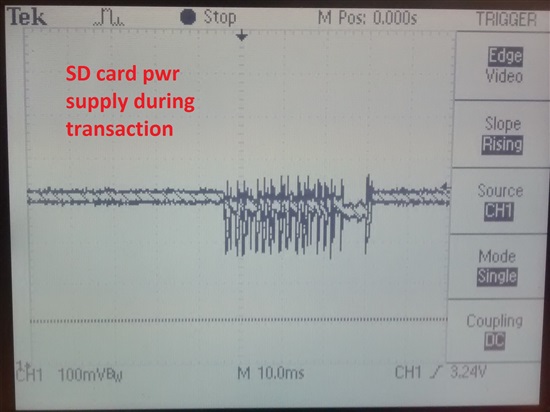

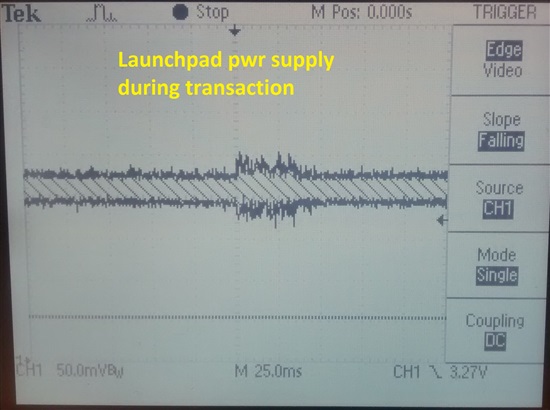

I have 8 channels of ADC (timer-triggered) sampling at high frequency. They directly signal the DMA to transfer in bursts to fill a large buffer. When the buffer is full, the DMA triggers a processing function which saves a portion of the data to SD. My problem is that during the 700us that the SDSPI is writing to SD, the data recorded by the ADC and transferred by DMA during those exact times is massively noisy, despite an oscilloscope indicating that the waveform should be pristinely clean.

In the images below: The blue shows a data compression of the ADC-measured waveform based on the orange, but it is corrupted during the sd writing (see orange excerpt for the actual high speed ADC data). The orange is clean on either side of that 700us.

I don't think it's an interference issue on the launchpad because my oscilloscope on the ADC line is perfectly clean and shows where I would expect the waveform to go.

I have also confirmed that the ADC channel integrity is maintained by the DMA, i.e. there isn't any mixing data between expected channels.

So I am puzzled by this noise which only happens during the time that the SDSPI is writing to the SD card.

ADC channel use:

ADCSequenceStepConfigure(ADC0_BASE, 0, 0, ADC_CTL_CH0); //PE3

ADCSequenceStepConfigure(ADC0_BASE, 0, 1, ADC_CTL_CH1); //PE2

ADCSequenceStepConfigure(ADC0_BASE, 0, 2, ADC_CTL_CH2); //PE1

ADCSequenceStepConfigure(ADC0_BASE, 0, 3, ADC_CTL_CH3/* | ADC_CTL_IE*/);//PE0 ("P30")

ADCSequenceStepConfigure(ADC0_BASE, 0, 4, ADC_CTL_CH4); //PD3

ADCSequenceStepConfigure(ADC0_BASE, 0, 5, ADC_CTL_CH5); //PD2

ADCSequenceStepConfigure(ADC0_BASE, 0, 6, ADC_CTL_CH8); //PE5

ADCSequenceStepConfigure(ADC0_BASE, 0, 7, ADC_CTL_CH9 | ADC_CTL_IE | ADC_CTL_END); //PE4

SDSPI config:

SSI2_BASE, /* SPI base address */

GPIO_PORTB_BASE, /* The GPIO port used for the SPI pins */

GPIO_PIN_4, /* SCK */

GPIO_PIN_6, /* MISO */

GPIO_PIN_7, /* MOSI */

GPIO_PORTB_BASE, /* Chip select port */ /* Was Port A! */

GPIO_PIN_5, /* Chip select pin */

GPIO_PORTB_BASE, /* GPIO TX port */

GPIO_PIN_7, /* GPIO TX pin */

DMA config:

uDMAChannelAttributeDisable(UDMA_CHANNEL_ADC0, UDMA_ATTR_ALTSELECT | UDMA_ATTR_HIGH_PRIORITY | UDMA_ATTR_REQMASK); //Set the uDMA channel for ADC to be high priority uDMAChannelAttributeEnable(UDMA_CHANNEL_ADC0, UDMA_ATTR_HIGH_PRIORITY | UDMA_ATTR_USEBURST/*|UDMA_ATTR_REQMASK*/); //Set data size and increment size plus uDMAChannelControlSet(UDMA_CHANNEL_ADC0 | UDMA_PRI_SELECT, UDMA_SIZE_32 | UDMA_SRC_INC_NONE | UDMA_DST_INC_32 | UDMA_ARB_8);//arb 4 may cause chans 0-3 to be in positions 4-8 as well //Set data size and increment size plus (alternate) uDMAChannelControlSet(UDMA_CHANNEL_ADC0 | UDMA_ALT_SELECT, UDMA_SIZE_32 | UDMA_SRC_INC_NONE | UDMA_DST_INC_32 | UDMA_ARB_8); uDMAChannelAssign(UDMA_CH14_ADC0_0); //Default? uDMAChannelTransferSet(UDMA_CHANNEL_ADC0 | UDMA_PRI_SELECT, UDMA_MODE_PINGPONG, (void *) (ADC0_BASE + ADCSSFIFO0),(void *) (HFS_ADC0_BuffA_Get()), DMA_TRANSFER_SIZE); uDMAChannelTransferSet(UDMA_CHANNEL_ADC0 | UDMA_ALT_SELECT, UDMA_MODE_PINGPONG, (void *) (ADC0_BASE + ADCSSFIFO0),(void *) (HFS_ADC0_BuffB_Get()), DMA_TRANSFER_SIZE); uDMAChannelEnable(UDMA_CHANNEL_ADC0);