Hi,

My customer is using EPI Hostbus 16bit mode. when they are writing, CS signal and WRn signal falls simultanously. However, when they are reading, RDn signal falls after one cycle CS falls. Is this normal? What sholud I do to make there is no delay?

Here is the code they used to set EPI:

EPIModeSet(EPI0_BASE, EPI_MODE_HB16);

EPIDividerSet(EPI0_BASE, 0x1);

EPIConfigHB16CSSet(EPI0_BASE, 0 , ( EPI_HB16_MODE_ADMUX |

EPI_HB16_CSCFG_ALE_SINGLE_CS |

// EPI_HB16_CSCFG_ALE_QUAD_CS |

EPI_HB16_BURST_TRAFFIC |

EPI_HB16_WRWAIT_3 |

EPI_HB16_RDWAIT_3 |

// EPI_HB16_MODE_FIFO |

EPI_HB16_WORD_ACCESS |

// EPI_HB16_CSCFG_ALE_DUAL_CS |

EPI_HB16_CSBAUD |

EPI_HB16_CLOCK_GATE_IDLE |

EPI_HB16_BSEL));

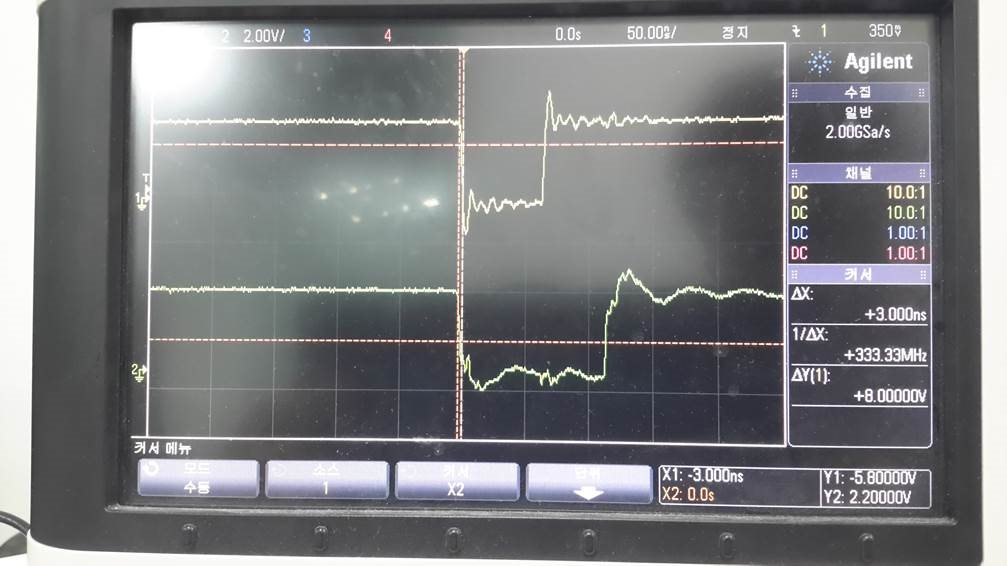

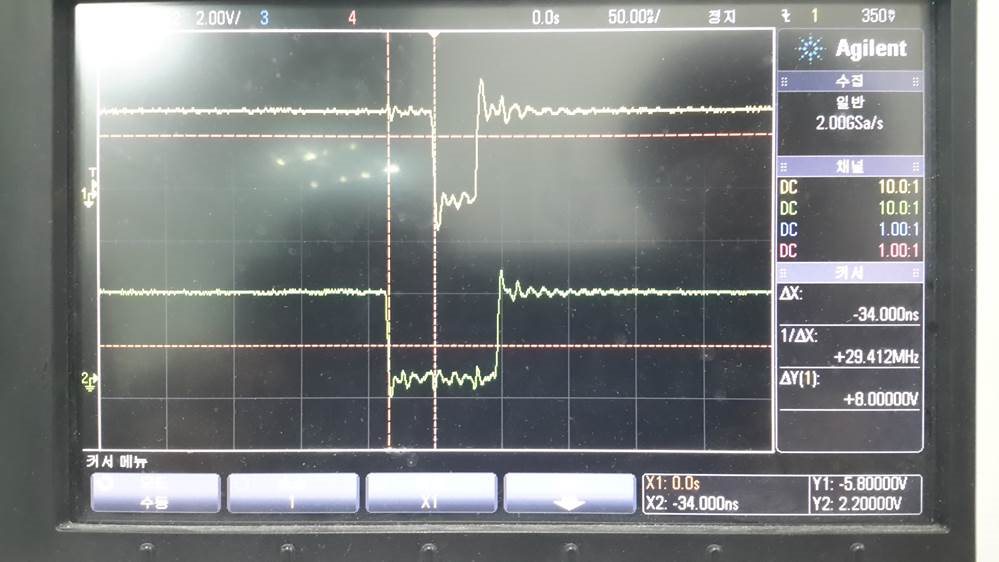

These are timing diagrams for writing and reading

-Writing(WRn - Yellow, CS - Green)

-Reading(RDn - Yellow, CS - Green)

Best Regards,

Ted