Other Parts Discussed in Thread: TM4C1294NCPDT, TPS22969

Hi Champs,

My customer set up a test procedure which power on/off M4. Power up cycle is 1s. They configure PQ4 as DIVSCLK output. They monitor the PQ4 clock. Normally, PQ4 clock will be 1.2Mhz because sysclk is 120Mhz and DIVSCLK = 99

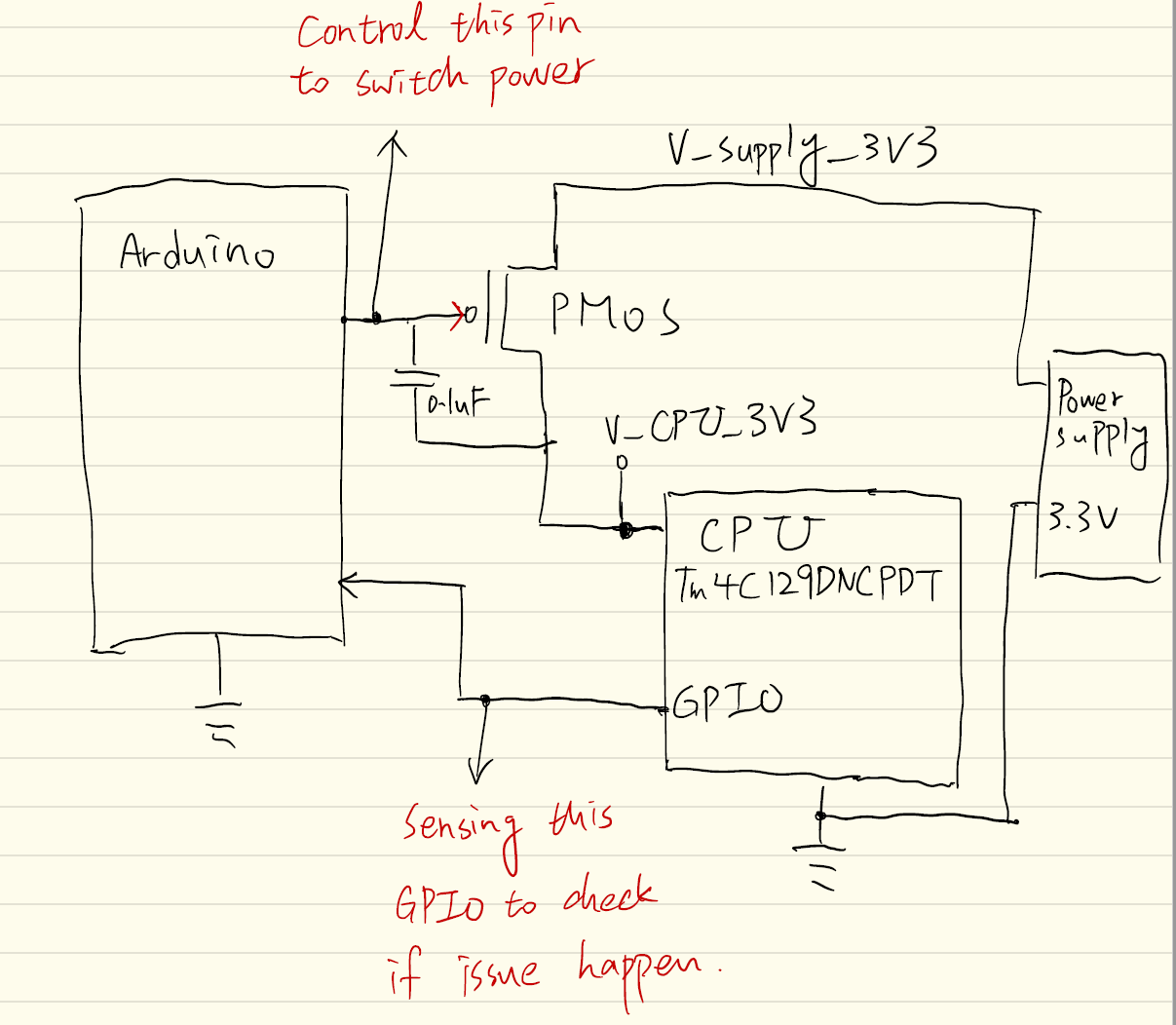

Customer test procedure is shown below.

1. Using Arduino to do shutdown test

2. When Tm4c129DNCPDT V_3V3 rising, Arduino start to count 65ms

3. After 65ms, Arduino detect an GPIO which is assigned by FW, if the GPIO still in LOW

state, Arduino will keep V_3V3 to wait for debug.

-> Because if sysclk is 120Mhz, GPIO will be pull high before 65ms. If GPIO is still low after 65ms, it means sysclk be changed

4. If GPIO in HIGH state, Arduino will shut-down the V_3V3 and do the Step 2~ Step 3 at a period 1sec again until issue happen.

5. GPIO PQ4 is used to detect the internal system clock

.

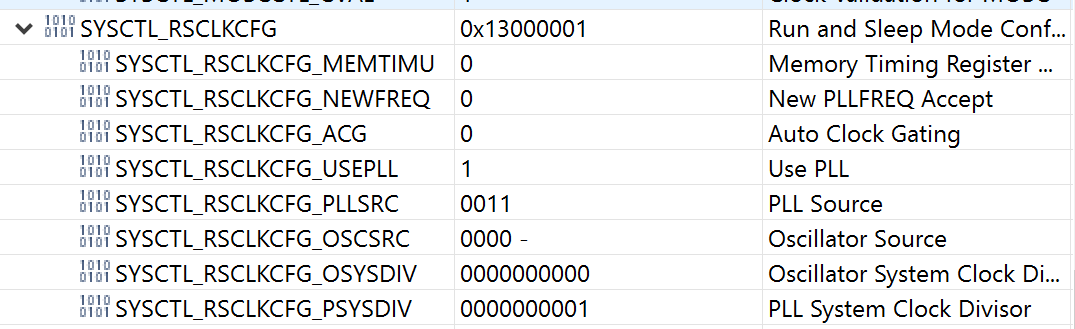

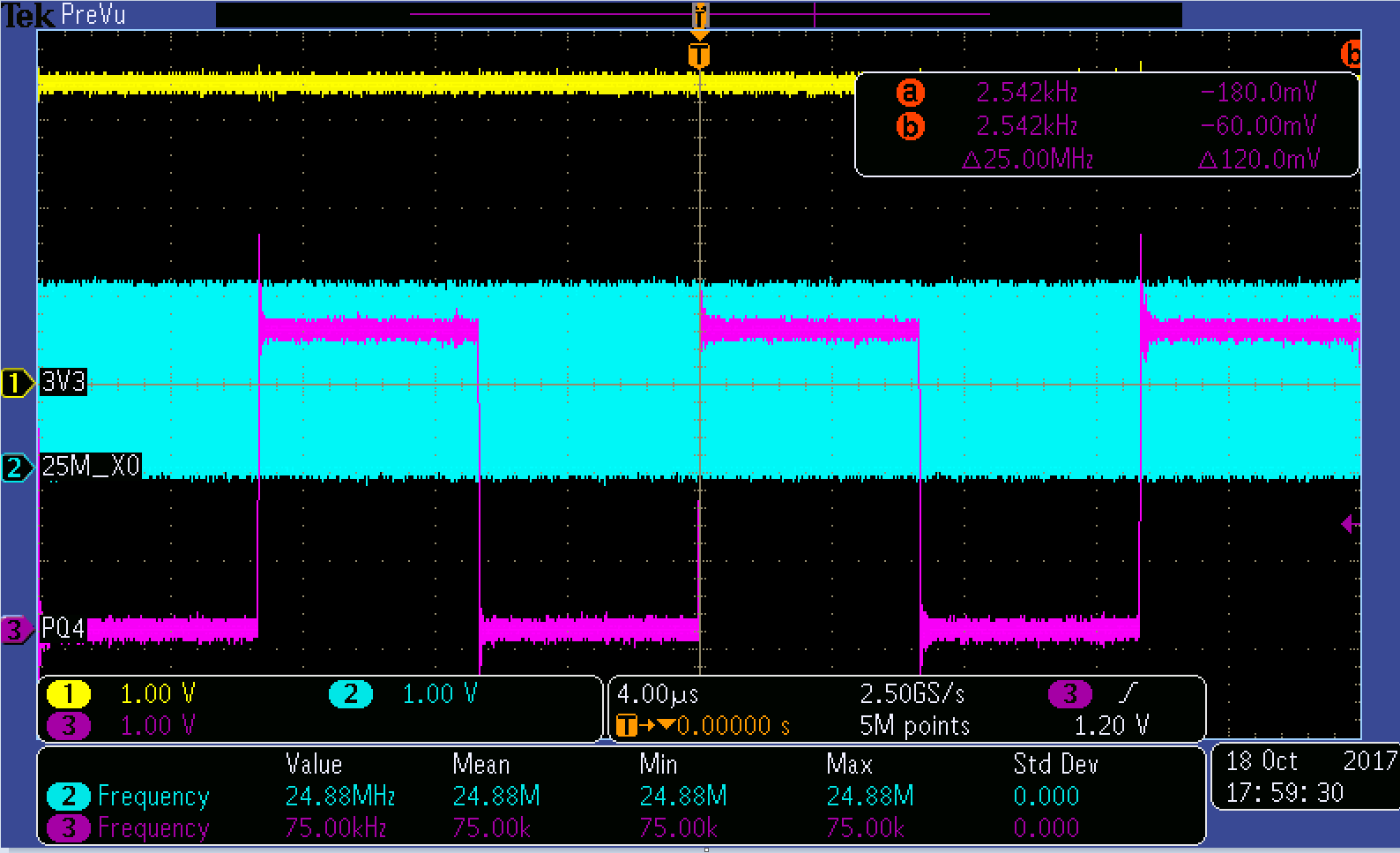

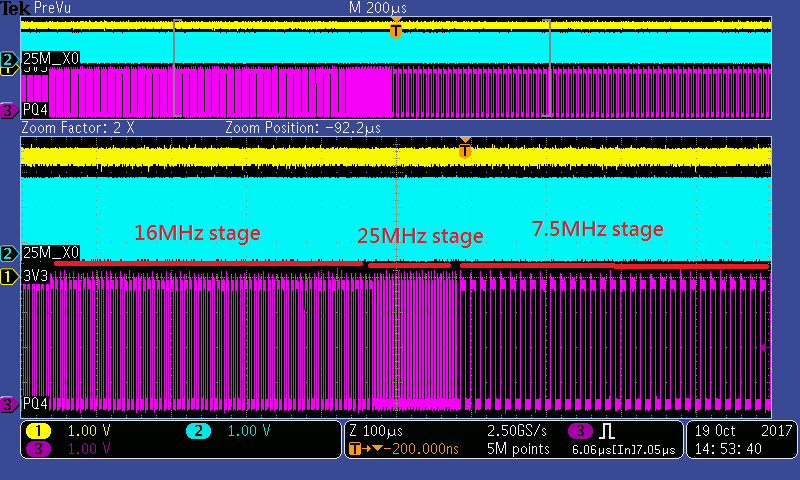

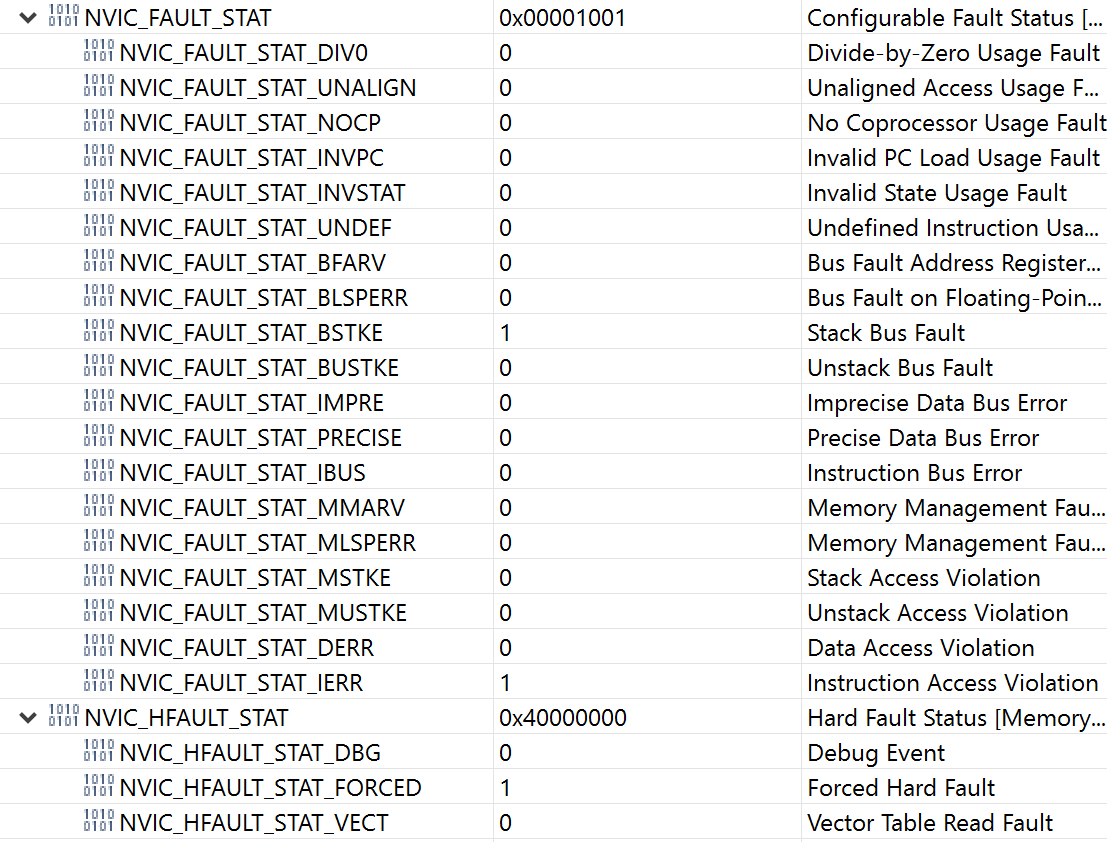

when issue happened, frequency of PQ4 is 75kHz which means sysclk is 7.5Mhz. Fvco=240, 7.5Mhz= 240/32. Looks like PSYSDIV =32. I connected ICDI to check internal SYSCTL_RSCLKCFG & STSCLT_PLLFREQ0/Q1. The setting is shown below. However, PSYSDIV is 0x1. I also check XTAL which still generate 25Mhz clock.

Another thing is that when I rewrite PSYDIV = 2 and PQ4 output frequency become 0.6Mhz. then I rewrote PSYDIV=1, PQ4 clock frequency become 1.2Mhz. It looks like system didn’t load correct value into PSYDIV. When we check errata, we found out that sysctl#22 which mentioned PSYDIV value may not be loaded into the physical divider causing the system clock to be divided by 2.

We thought will this related with this errata. Could you please help on this ? thanks !

Customer also want to know what is the difference between TM4C1294NCPDT and TM4C129DNCPDT. They faced sysclk issue before on TM4C129DNCDPT and they try to duplicate issue on Launchpad which use TM4C1294NCPDT. They can’t duplicate issue, however, issue happened when they change IC to TM4C129DNCPDT. Thanks!

Register setting

PQ4 output waveform