Tool/software: Linux

Hi,

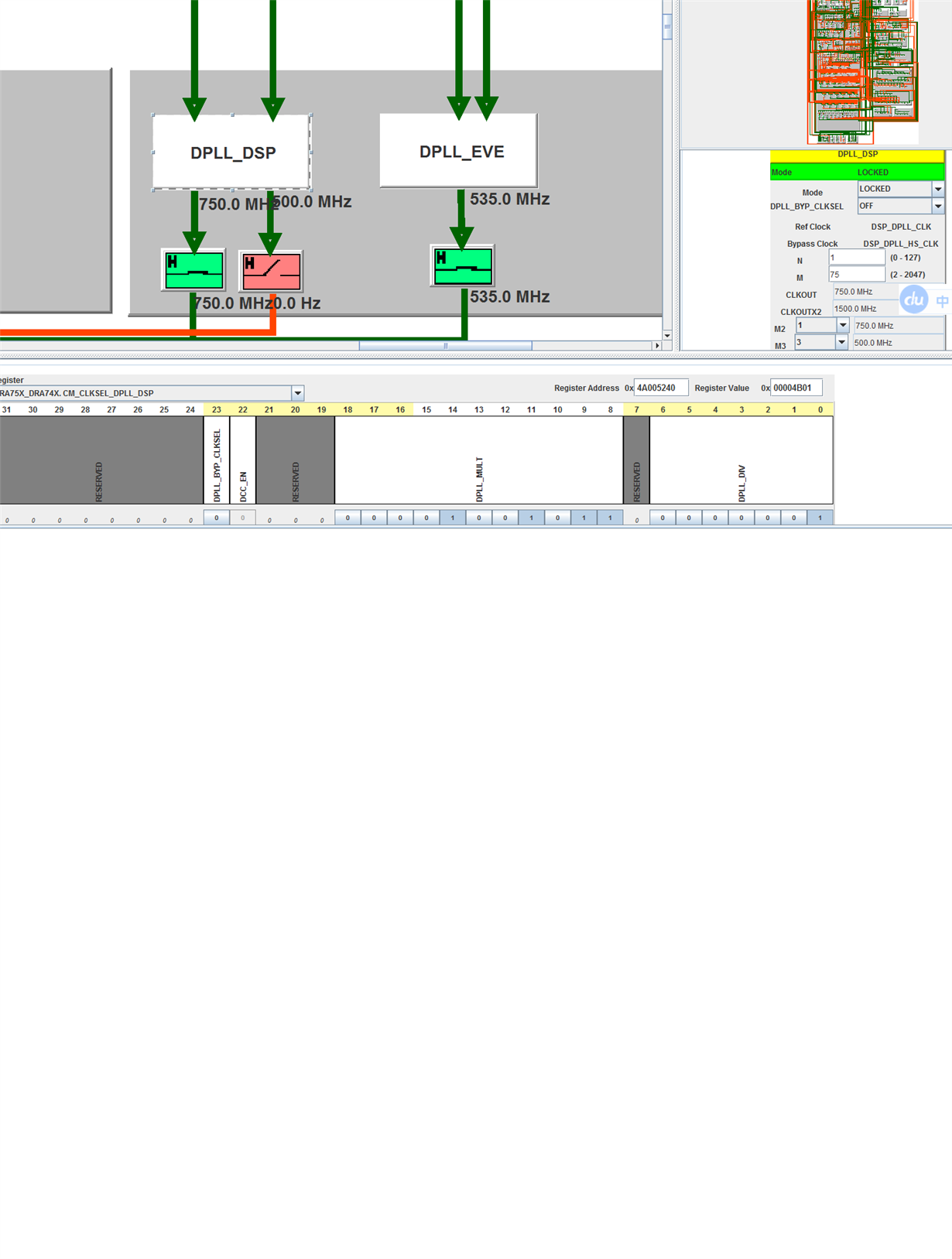

The J6 (DRA756) kernel we used is version 4.4.84, and the DSP clock was configured to 700M in uboot and changed to 600M under the kernel.

I modified kernel code,but did not realize the 700M clock, modify the following code. Is there any problem with my change? Is there anything else that needs to be changed?

Thank you.

arch\arm\boot\dts\dra7xx-clocks.dtsi

dsp_dpll_hs_clk_div: dsp_dpll_hs_clk_div {

#clock-cells = <0>;

compatible = "fixed-factor-clock";

clocks = <&dpll_core_h12x2_ck>;

clock-mult = <175>;

clock-div = <4>;

};

dpll_dsp_byp_mux: dpll_dsp_byp_mux {

#clock-cells = <0>;

compatible = "ti,mux-clock";

clocks = <&sys_clkin1>, <&dsp_dpll_hs_clk_div>;

ti,bit-shift = <23>;

reg = <0x0240>;

};

dpll_dsp_ck: dpll_dsp_ck {

#clock-cells = <0>;

compatible = "ti,omap4-dpll-clock";

clocks = <&sys_clkin1>, <&dpll_dsp_byp_mux>;

reg = <0x0234>, <0x0238>, <0x0240>, <0x023c>;

assigned-clocks = <&dpll_dsp_ck>;

assigned-clock-rates = <700000000>;

};

dpll_dsp_m2_ck: dpll_dsp_m2_ck {

#clock-cells = <0>;

compatible = "ti,divider-clock";

clocks = <&dpll_dsp_ck>;

ti,max-div = <31>;

ti,autoidle-shift = <8>;

reg = <0x0244>;

ti,index-starts-at-one;

ti,invert-autoidle-bit;

assigned-clocks = <&dpll_dsp_m2_ck>;

assigned-clock-rates = <700000000>;

};

dpll_dsp_m3x2_ck: dpll_dsp_m3x2_ck {

#clock-cells = <0>;

compatible = "ti,divider-clock";

clocks = <&dpll_dsp_x2_ck>;

ti,max-div = <31>;

ti,autoidle-shift = <8>;

reg = <0x0248>;

ti,index-starts-at-one;

ti,invert-autoidle-bit;

assigned-clocks = <&dpll_dsp_m3x2_ck>;

assigned-clock-rates = <466666667>;

};