Dear, Sir.

My customer would like to monitor nFAULT=Low to High changing status during power-up

and then, start SPI communication for resister setting.

So I would like to make sure several as below. Please give your advice.

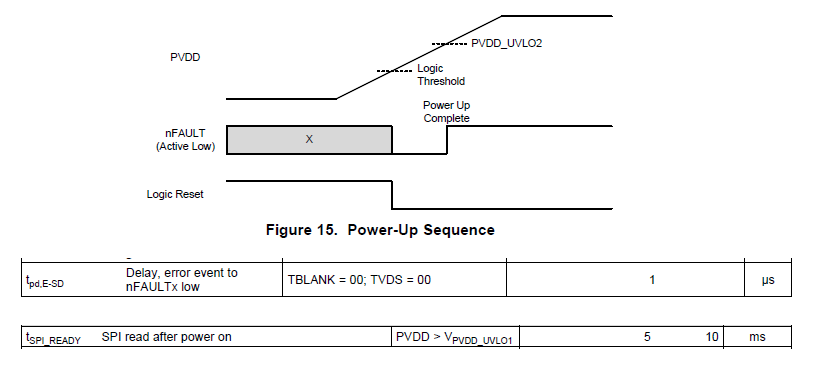

1. nFAULT Delay, across PVDD_UVLO2 to nFAULT=>High.

The situation is diffrent, but tPD, E-SD is defined as max. 1us.

I guess max. 1us would be enough as this kind of delay.

How do you think?

2. tSPI_READY is defined as max. 10ms. It is after PVDD>VPVDD_UVLO1.

The customer will monitor the change state nFAULT Low to High.

I guess max. 10ms delay would be safer starting SPI communication.

How do you think?

Best Regards,

H. Sakai