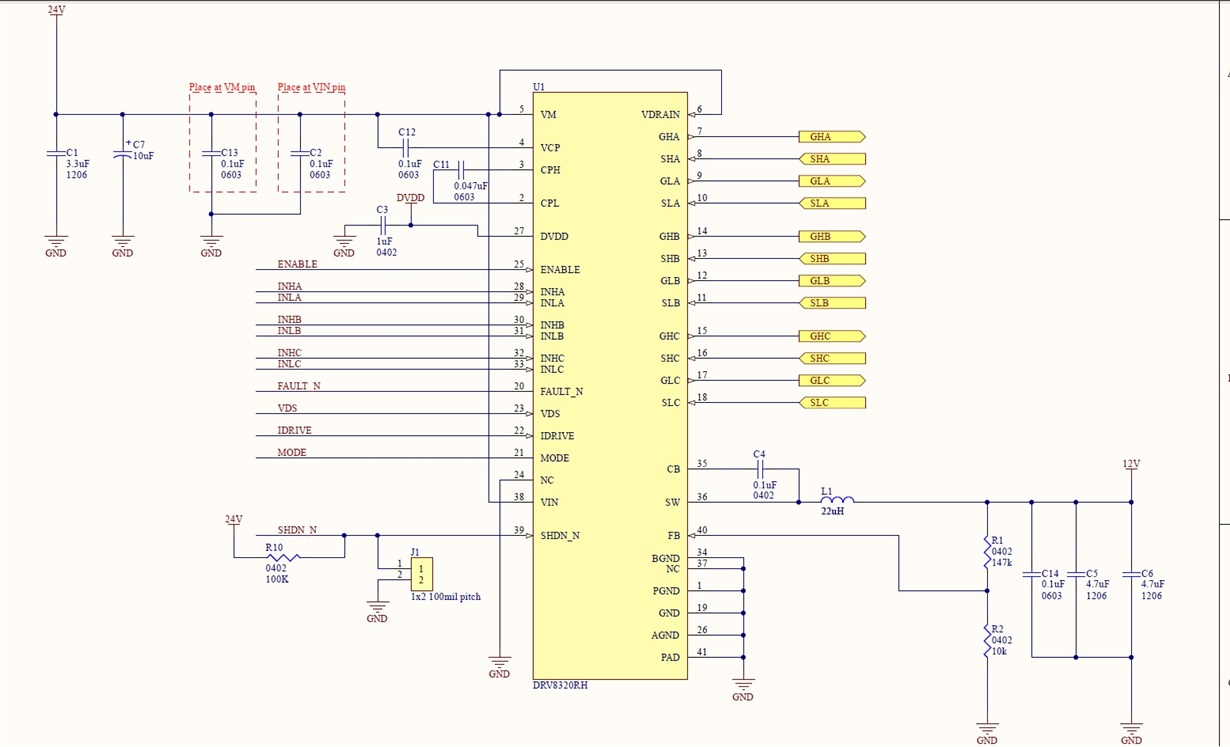

Other Parts Discussed in Thread: DRV8320

Hello,

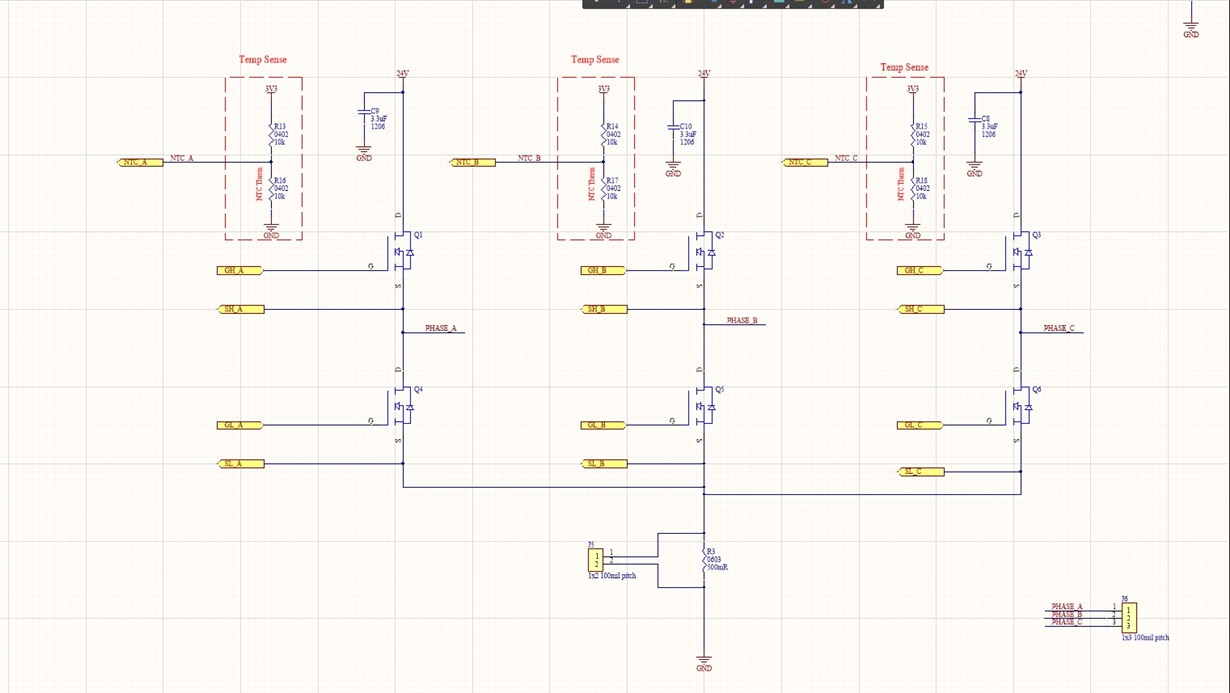

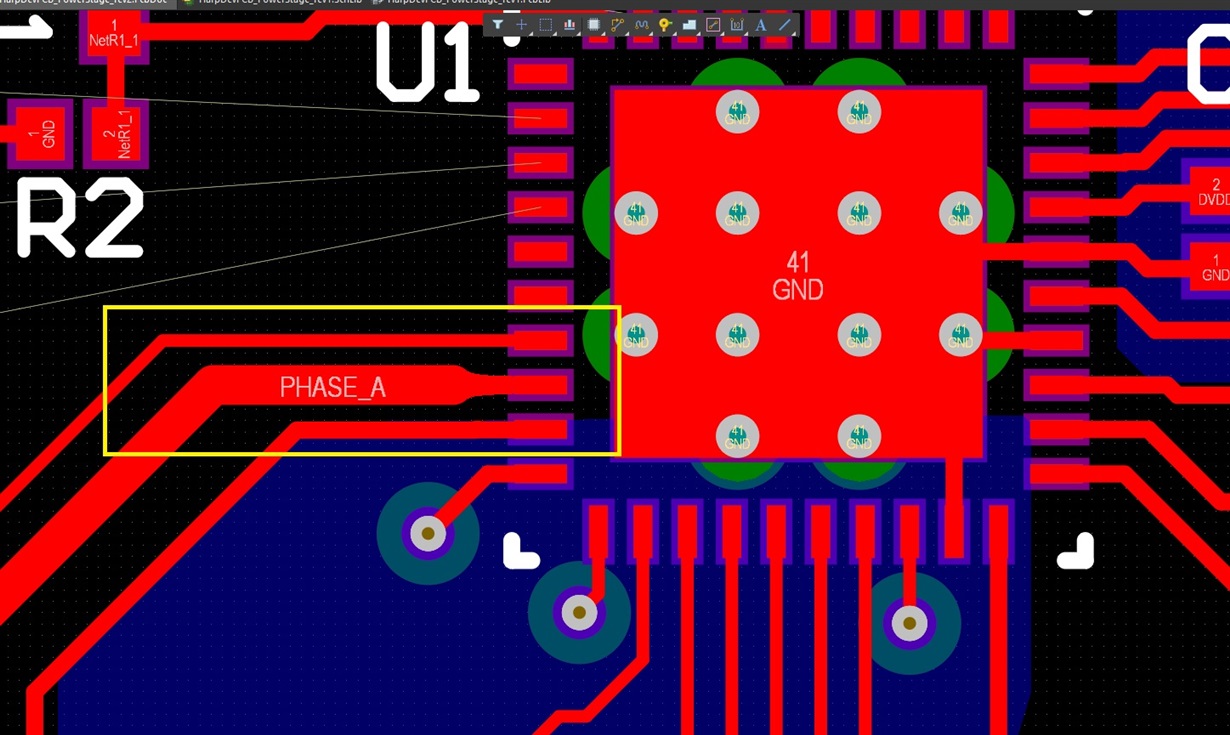

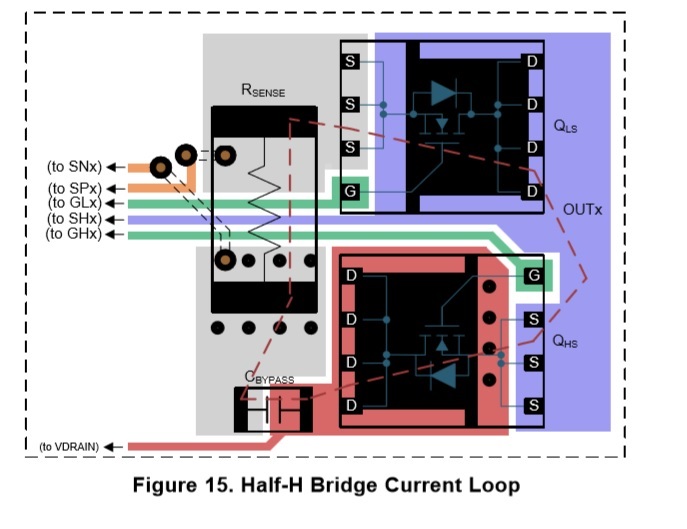

In reading through the datasheet for this part (hardware version with the buck regulator) I don't see any recommendations on the overall grounding scheme between AGND, PGND, GND and PAD. All I've gathered is that AGND is for the DVDD linear in case you need a quiet low current supply?

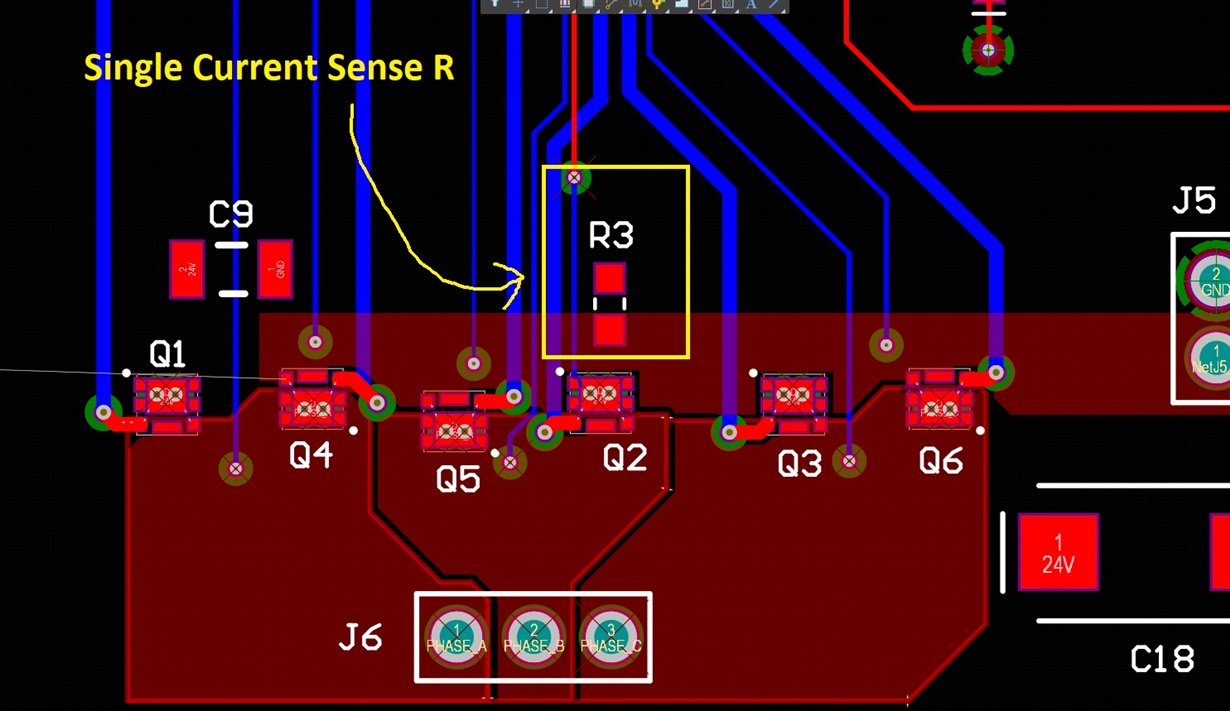

1. Could someone clarify how I should connect up the AGND, PGND and GND relative to one another?

1a. should all the ground be connected together if I don't need the DVDD output?

2. Is it correct to connect the thermal pad to the "gnd" net?