Dear, Sir.

My customer will start the design to apply DRV10987 for their system.

In advance, they would like to make sure following topics.

Please give your advice.

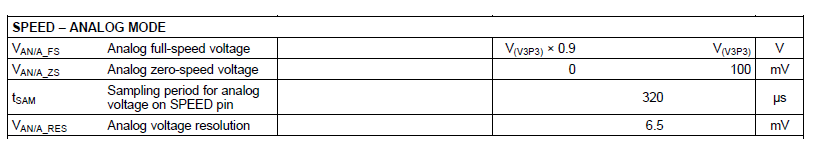

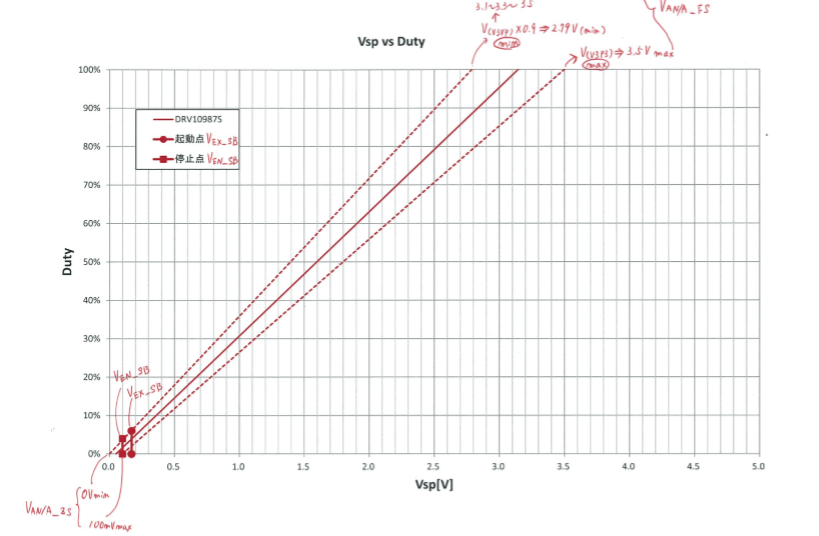

1. Full-speed voltage & Zero-speed Volatge.

It will be defined on the datasheet, 0.1V to 0.9* 3.3v.

I am not sure the real resolution of internal ADC, but I wonder the

lower reading values & higher reading values would be conveted to Full & Zero?

2. Resolution.

It will be defined, typ. 6.5mV.

I wonder the resolution will be reflected the error like INL, DNL?

If you know like ENOB, Please advice me.

Best Regards,

H. Sakai