Hi Team,

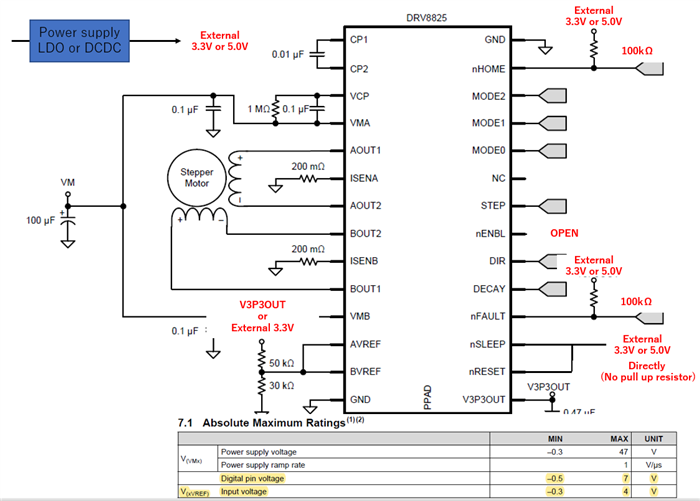

We don't use V3P3OUT (3.3V) for VREF and other circuit.

Because, our load current is more than 1mA.

Therefore, we use the external 3.3V or 5.0V(without VREF) by LDO or DCDC.

Then, is there a recommended power supply sequence?

(For example, 3.3V or 5.0V must be less than VM voltage etc.)

According to the Absolute Maximum Ratings of Digital pin voltage and V(xREF) input voltage is 7V(max) and 4V(max).

So, I understand that there isn't the limit for Power supply sequence.

Is my understanding correct?

Regards,

Hide