Other Parts Discussed in Thread: DRV8703-Q1

Hi,

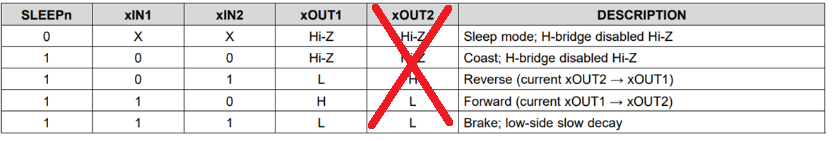

I m planning to use DRV8704 for one of my projects. I m curious to know how DRV handles PWM input. Will it produce complementary signal on the output for a specific half bridge to handle or is it mirored pwm signal for one high side FET and one low side FET?. If i send one edge aligned PWM signal on AIN1 with 30% duty cycle what will be the output on A1HS, A1LS, A2HS and A2LS?