Dear, Sir.

My customer is about following questions.

Sorry to disturb your job, but Please give your advice.

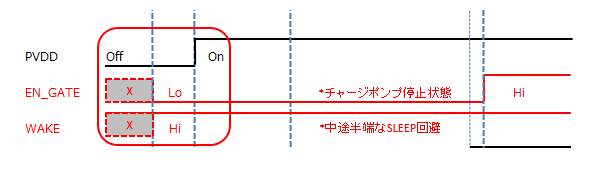

1. Is there the deday time definition on WAKE signal low to high after PVDD power-up?

2. Is there the delay time definition on EN_GATE signal low to high after PVDD power-up?

Best Regards,

H. Sakai