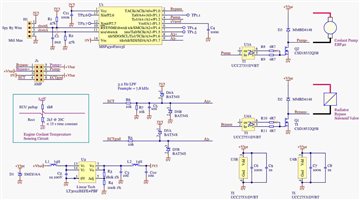

Other Parts Discussed in Thread: MSP430F2013, MSP-FET

I've just blown up a UC27531 and I am at a loss as to the reason why. It's the first time I have used this driver so I have no experience with it at all.

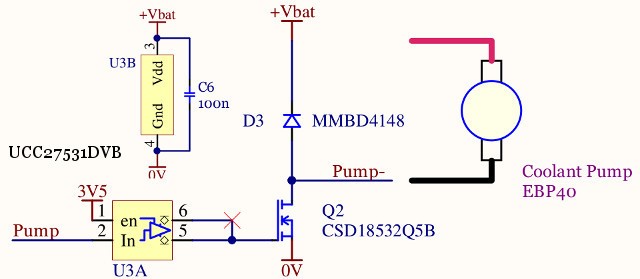

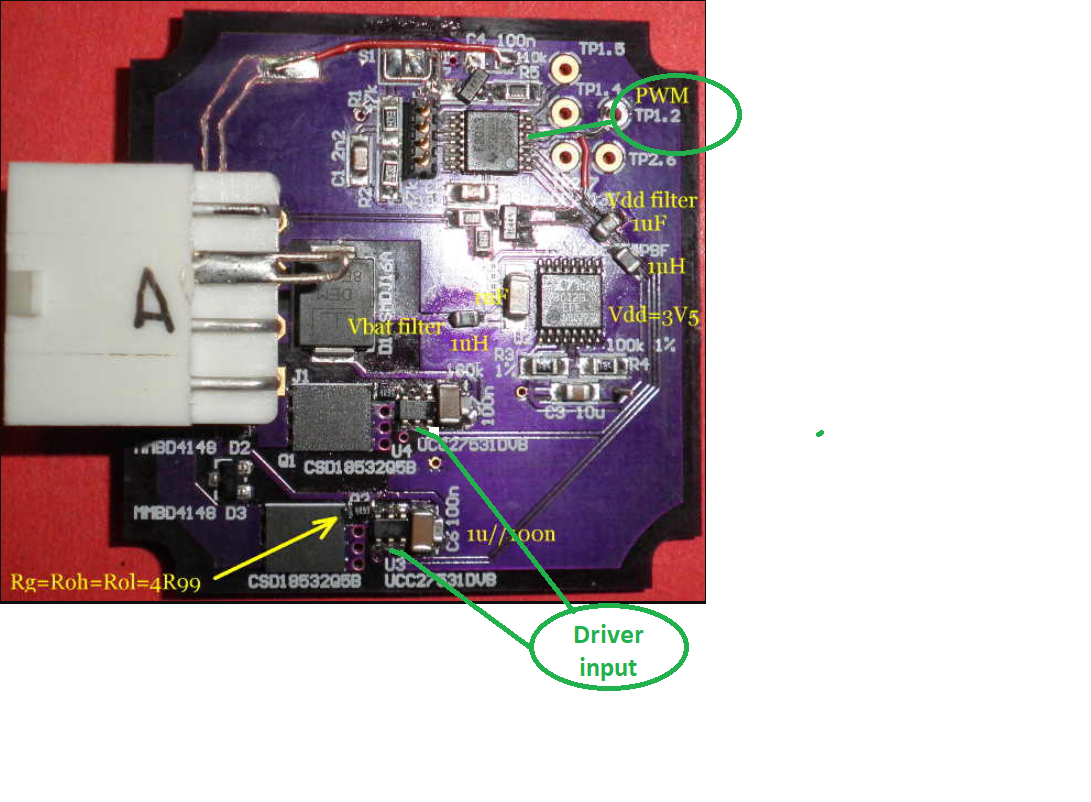

The circuit :-

The "Pump" PWM signal is driven from an MSP430F2013 port, at 25 kHz with a duty cycle of 14 to 100 %

+Vbat is a 12V battery, and the pump draws 5A pk. The motor is brushless with an internal controller of unknown design. It has been tested successfully on a commercial PWM driver.

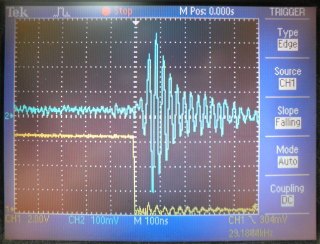

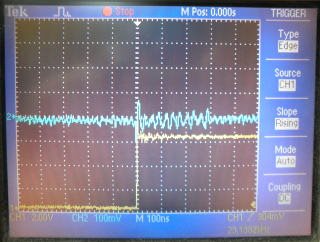

I have been testing the program/cicuit with a resistive load, but it failed withing seconds of turning it on. The MOSFET is fine, but the driver output is shorted to ground, I am at a loss as to the exact mechanism that killed the 2.5/5A device, but I assume it has something to do with the gate - drain Miller capacitance of Q2 and my lack of gate current limitation. I am surprised that the gate current could reach beyond 2.5A though, but admit that i did not do any calculations, in part because I don't know how.

I went to some trouble to follow the layout suggestions. In particular, the source and return traces (U3 - Q2) are parallel and their lengths are minimised. Similarly for the onboard traces to the pump.

Can someone explain the failure and suggest the design procedure that I should have used to prevent it?