Hi All, We are using this chip in a design for a sync interface unit and have picked up a problem that we have also reproduced on the LMH1980 EVAL board.

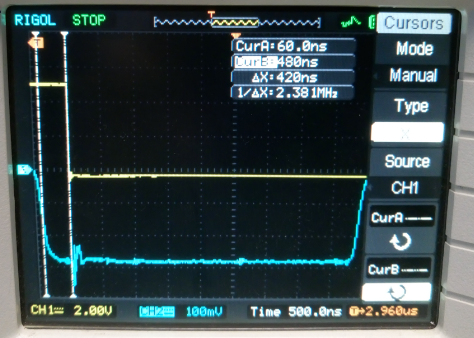

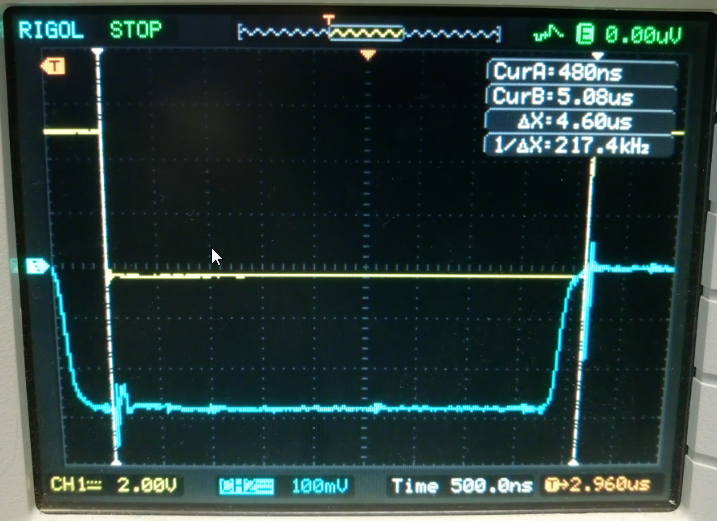

Input sync pulse are delayed about 700ns on the falling edge and only 200ns on the rising edge. The result of this is that the negative sync pulses (line sync, field sync and equalising pulses) are all about 500 ns below specification. E.g the line sync pulse is 4.2 us instead of 4.7us. Our application uses Stanag 3350 as a guide which requires a line sync pulse of 4.7us +/- 0.2 us.

On checking the datasheet we note that the latency is only specified with respect to the falling edge although the diagram does suggest that the rising edge latency is roughly the same as the falling edge latency.

We have not yet determined if this is only a spec issue or a real issue. We will only know that when we complete a system integration test. In the mean time if you could shed any light on this that would help us to mitigate any risk it would be much appreciated.

Thanks

David