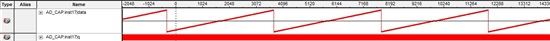

I set EN_RAMP to "1", cause all the channels to output a repeating full-scale ramp pattern, and use altlvds_rx in FPGA to receive the ramp signal, I can see the ramp pattern in Signal Tap,but the data is not all right, regularly three datas are the same after three datas increments as the figures below show.

When I put sine signal to AFE5805 input pin, the same phenomenon happens.What causes this phenomenon,AD converter or LVDS receive ?