Hi Team,

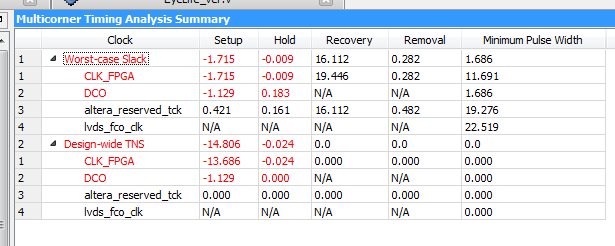

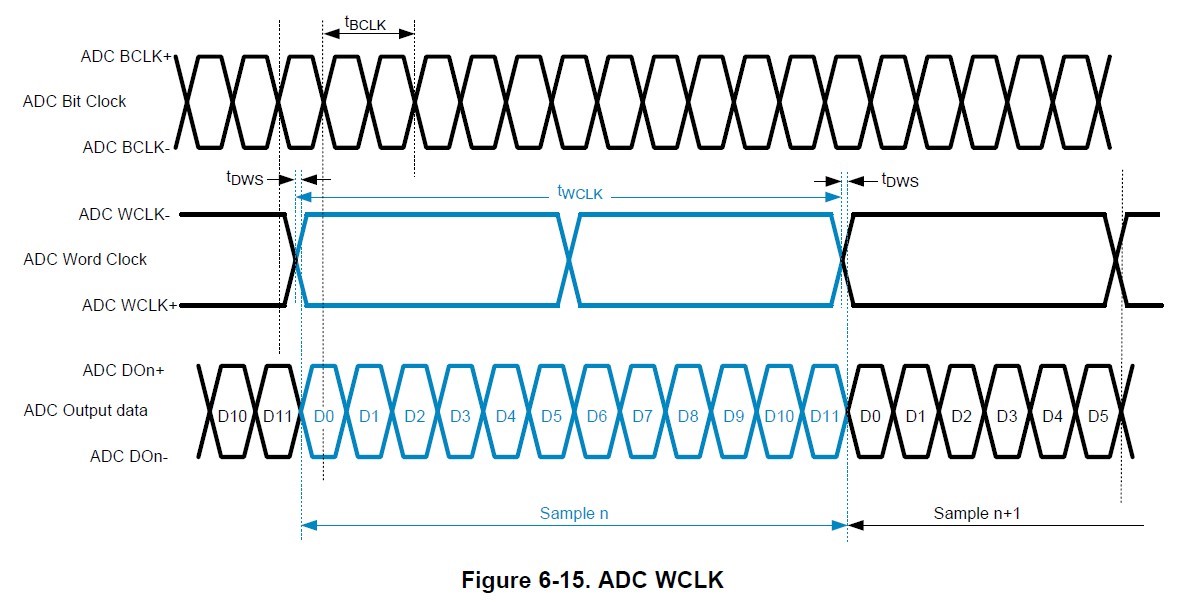

I am trying to figure out how bit clk and fclk are related on the LM96511. I am trying to include the FCO_CLK in the SDC file but I don't know why lvds_fco_clk is showing as N/A. Any guidance or documentation on how to setup these clocks?

Regards,