Hello,

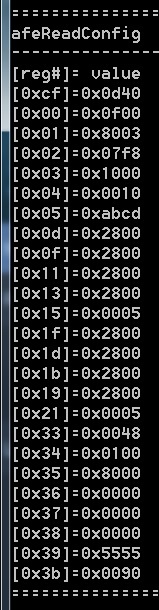

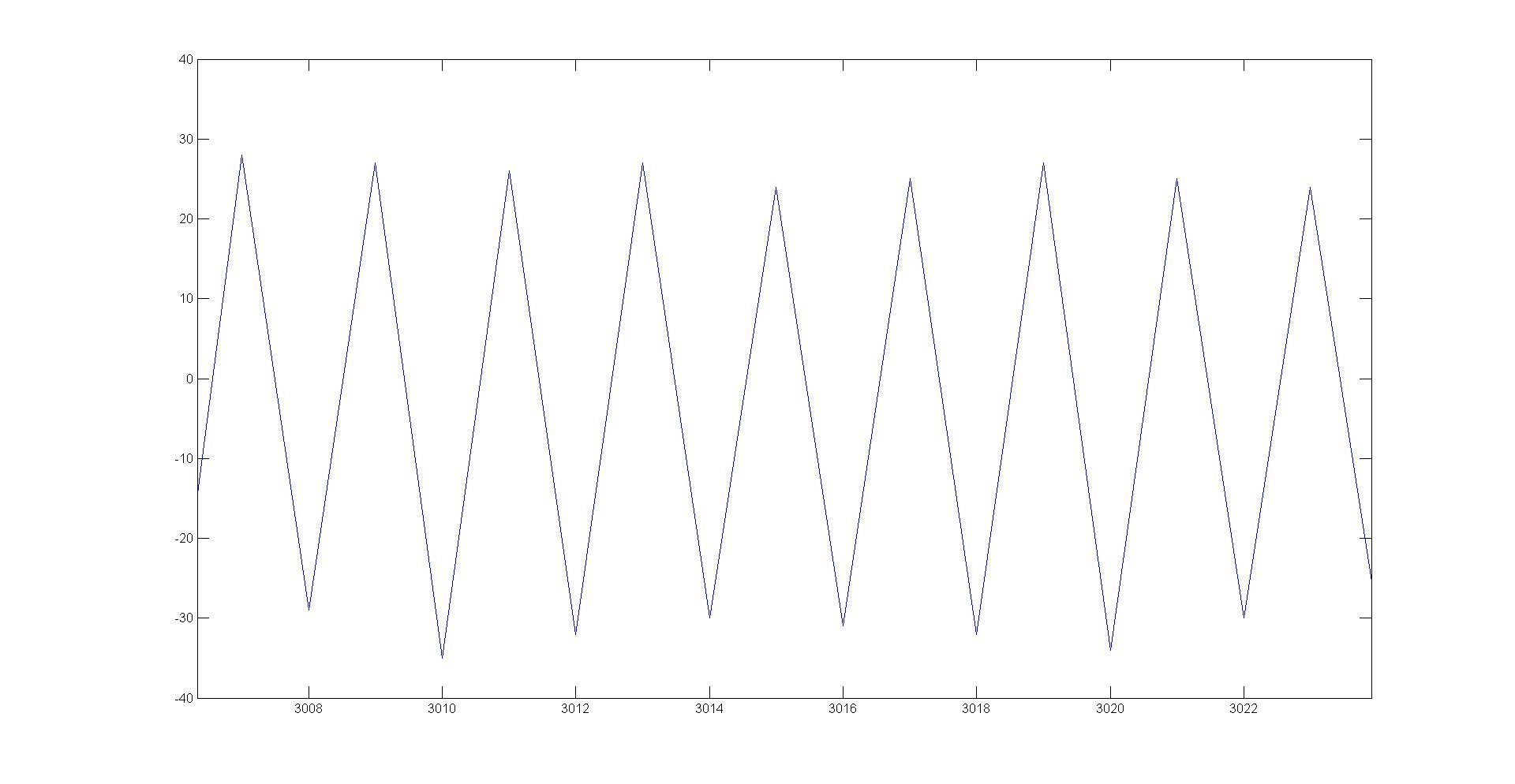

One of our customers is working on Analyzer equipment, using the AFE5808. The customer is experiencing some strange artefacts during the measurements. When using a 5mVpp sine wave 1.8MHz, a sine wave is seen (visualization using Matlab). See the attached image “Sinus 1.8 Mhz 0.005 Vpp.jpg#. When the input is terminated with 50Ω, noise (modulated by the clock, or alternating around zero every clock cycle). See the attached image “Alternating noise with 50 Ohm termination.jpg”.

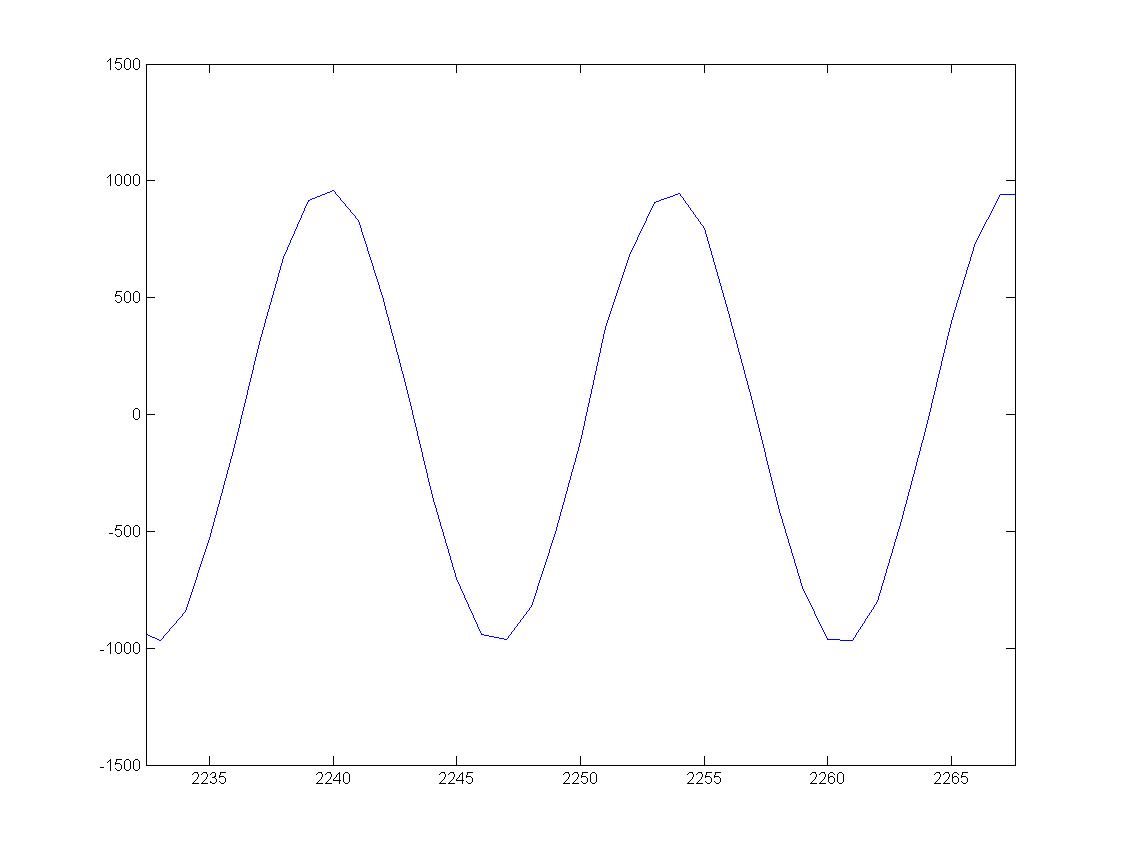

Attached an image of the AFE settings as well (“AFE Settings.jpg”).

What could be the cause of this artefact/problem. What can be done to solve it?

If you need more information, please let me know.

Regards,

Meir.