Hi,

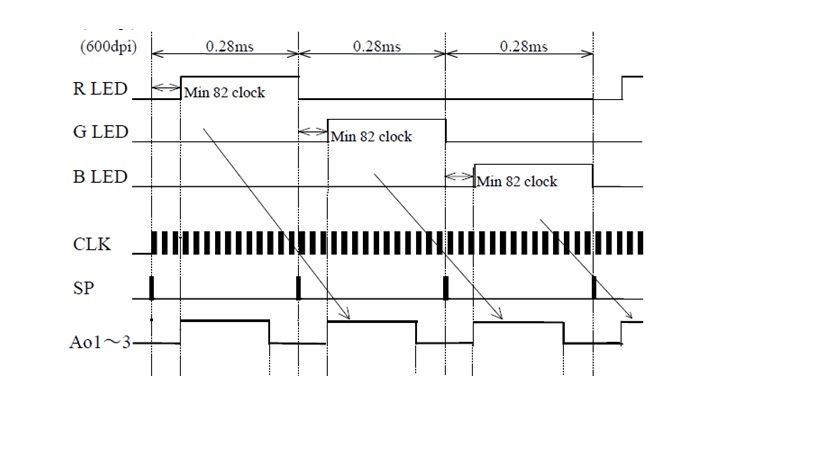

I am using Contact image sensor in my application, I am using LM98722 AFE to interface CIS sensor, i need help in CCD timing generation in LM98722 for providing clock signals to my CIS sensor..

I need to give 4 MHz clock input and 3.6 KHz clock input to my CIS Sensor, how can this two clock frequencies can be generated from LM98722 AFE CCD timing generation.

Thanks in Advance....

Regards,

Gokuleswaran R

Design Engineer