Hi team,

My customer evaluated TSC2046 and discovered an unexpected glitch occurring at DOUT.

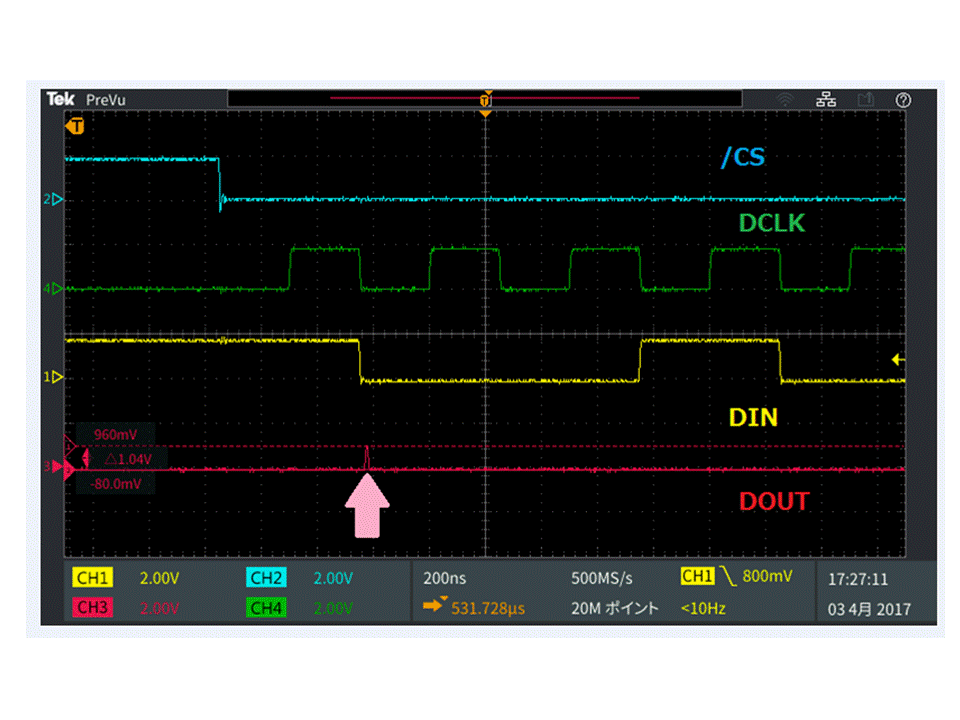

Please look at Fig-1 wave forms.

Fig-1. /CS,DCLK,DIN and DOUT with glitch wave forms

So, the customer made the following inquiries to us.

① What can be considered as a cause?

② Is there a possibility that the timing of this glitch changes greatly, and it violates

setup-and-hold timing of the communication partner?

③ What kind of countermeasures can be considered to eliminate this glitch?

Please let me know the answers.

Detailed information on the evaluation is below.

・The customer evaluated two TSC2046 samples. Both samples have the same phenomenon.

・Dout is connected only to CPU input.

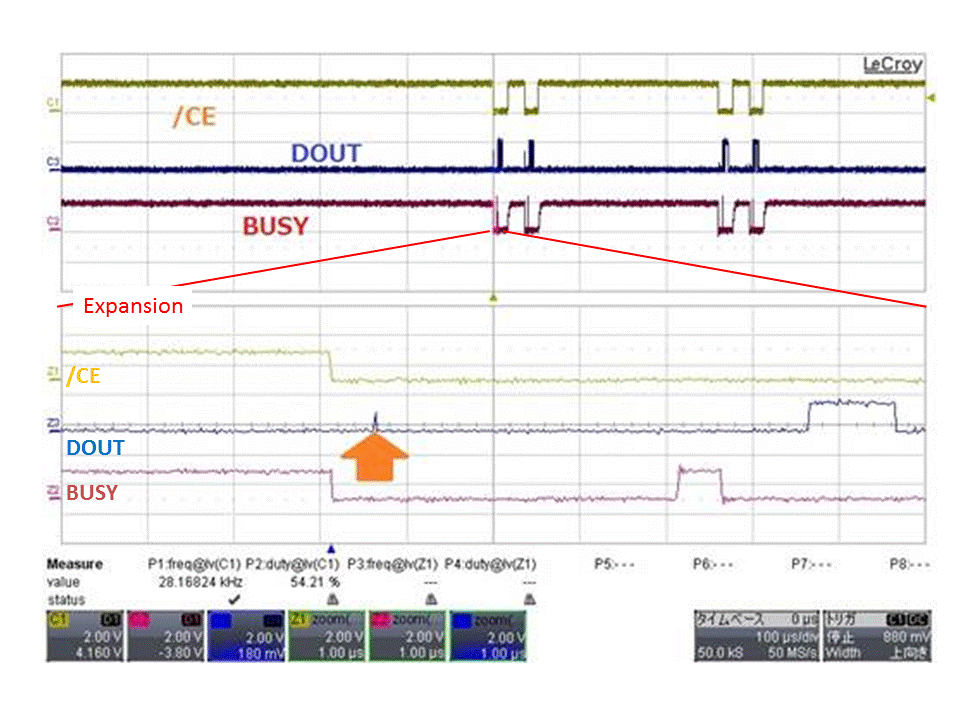

・The glitch occurs at the timing of the falling edge of the STARTbit of DIN at a

frequency of about 70%

・CS,BUSY and DOUT with glitch wave forms are bellow .

Fig-2 /CS,BUSY and DOUT with glitch wave forms

Best regards,

Fumio Nakano