Hello,

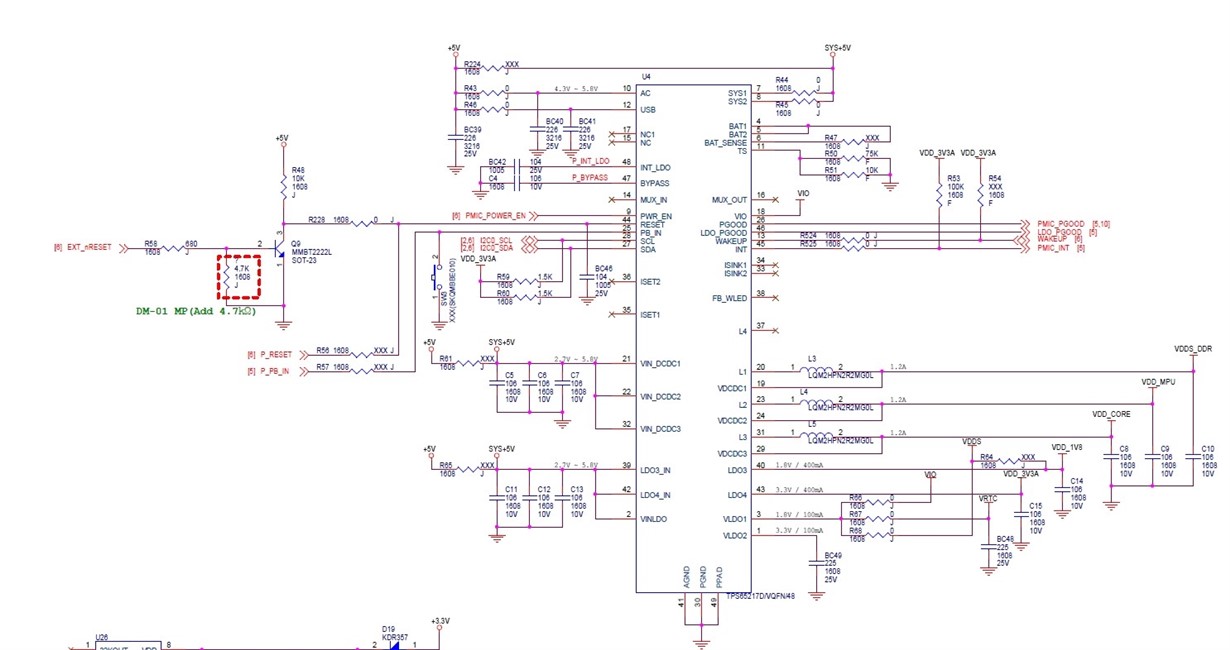

Customer made circuit as below, and under test.

During RESET TPS65217D, all power rail go to 0V, but only LDO4 doesn't go to 0V.

It remains as around 2.8V.

It happens even pull down RESET pin more than 1 seconds.

Could you check and let me know why LDO4 doesn't go to 0V while RESET?

Regards,

Nicky