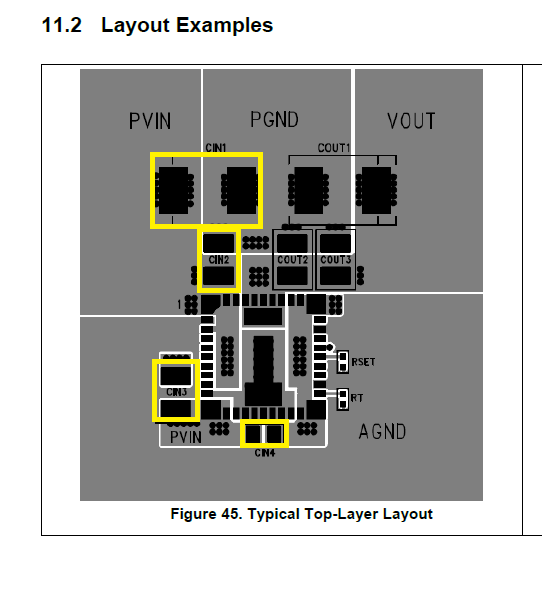

Hello I am designing in an LMZ31710 for my next PCB design. I am reviewing the recommended layout and I notice in figure 45 of the datasheet there is a cap marked cin4. I do not see any reference to cin4. Can you clarify this capacitor and its value please.

Regards,

Guy