Hi team,

My customer has some questions about the power sequence of tps659039, please help check:

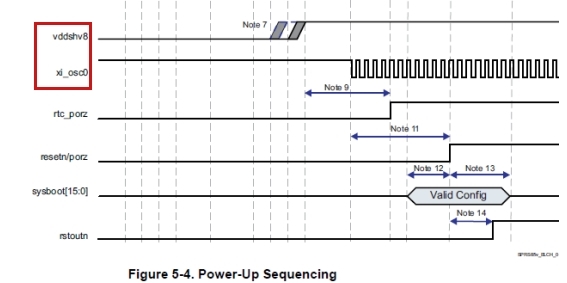

1. Xi-osc0 powers up 6.6ms ahead of vddshv8, which is different from the required power sequence? Is there any risk and how to improve?

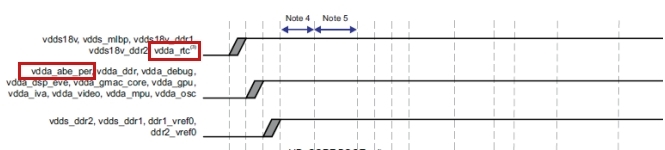

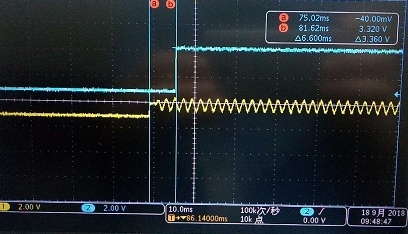

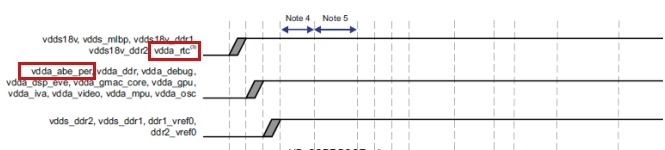

2. Similar issue for vdda-rtc and vdda-abe-per, the actual test show that vdda-abe-per is 0.58ms ahead of vdda-rtc.

OTP version is O9039A387IZWSRQ1. Thanks

Dongbao