Hello TI,

Seeking your help in understanding the few test parameters test methodology for UCC28C42 PWM controller.

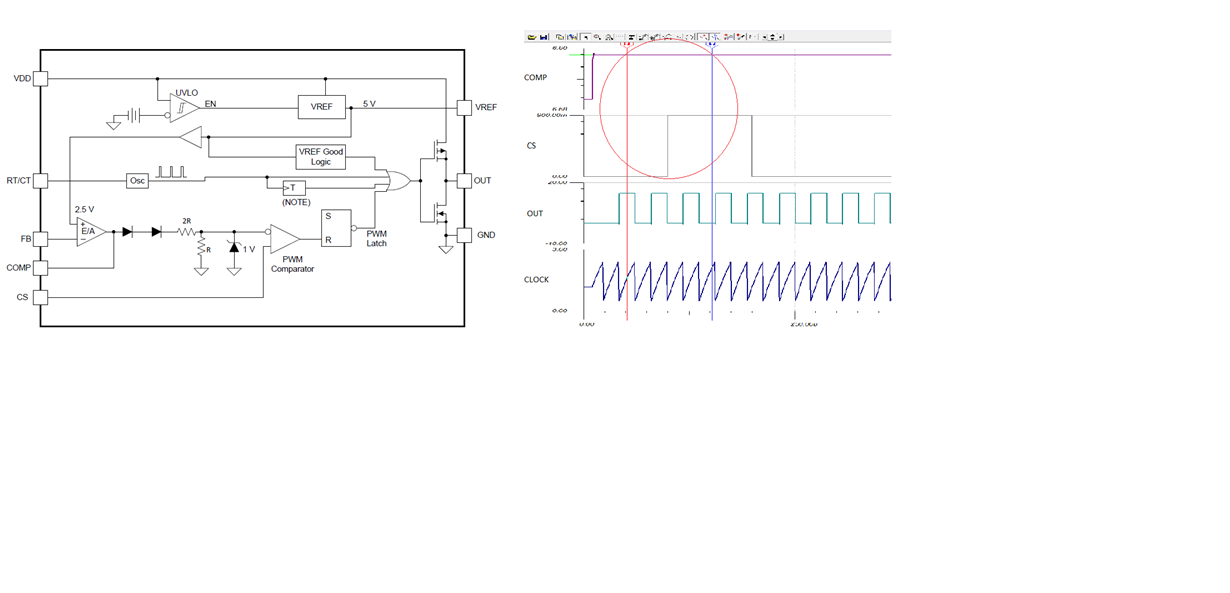

1. ACS (GAIN) of PWM Comparator. As test condition says at Vfb = 0V, vary the Vcs from 0V to 0.9V to measure voltage variation at COMP pin. But COMP output depends on CS input? Also I tried simulating in TINA with datasheet test condition and I don't see any voltage change at COMP pin.

Can you assist me how do I do this?

2. Open Loop Voltage gain for Error amplifier. can you illustrate the test method for this test with respect block diagram.

Regards,

Swamy M.