Hello.

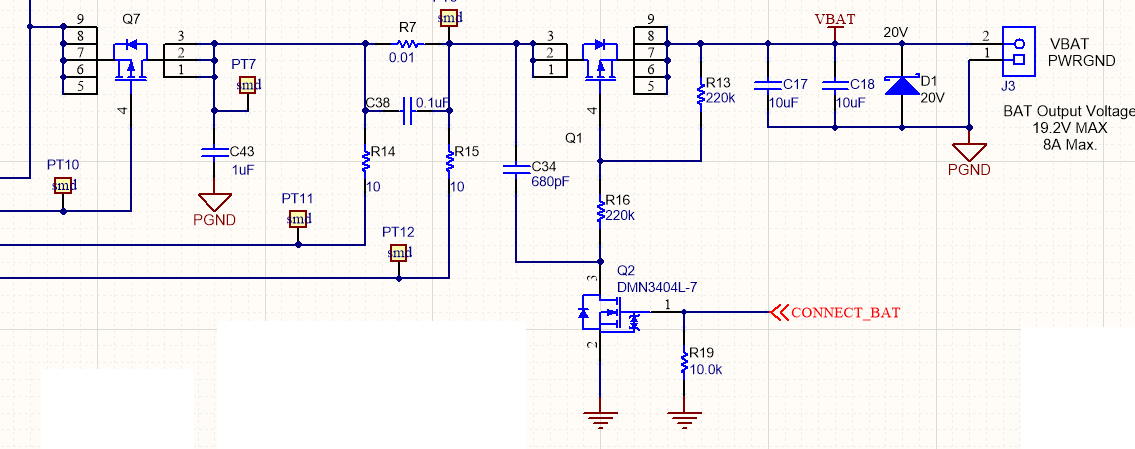

In my design, the battery will work as a backup to sustain device functioning for a while in case of mains fault. Equipement is powered off either by the operator or when battery is fully depleted. Once powered off, the equipment will be powered back on only when mains voltage is normal.

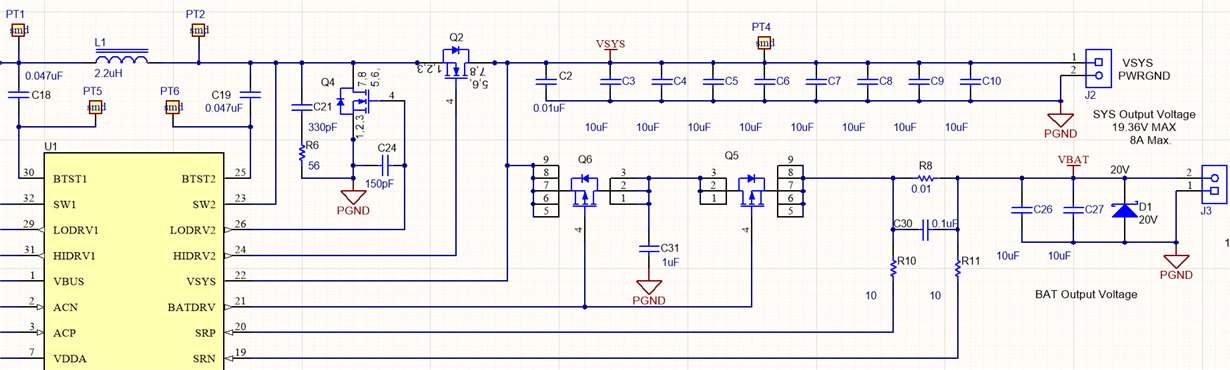

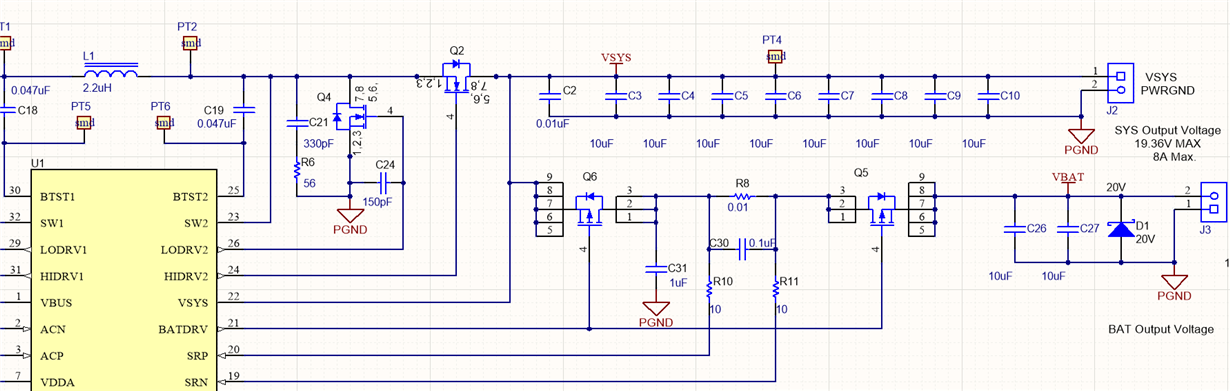

Could one of the configurations below work? The idea is that the microcontroller pulls down ILIM_HIZ to switch the power supply/charger off. The main idea is to reduce current drained from battery, especially when it reached the minimum charge.

If the above does not work, is there a simple way to achieve the same functionality?