I am designing a gate driver for sic mosfet module using the ucc2753x. The sic mosfet is powered by a positive and a negative bias. That means the GND pin must be negative, however all the input signals of ucc2753x are reference to this node.

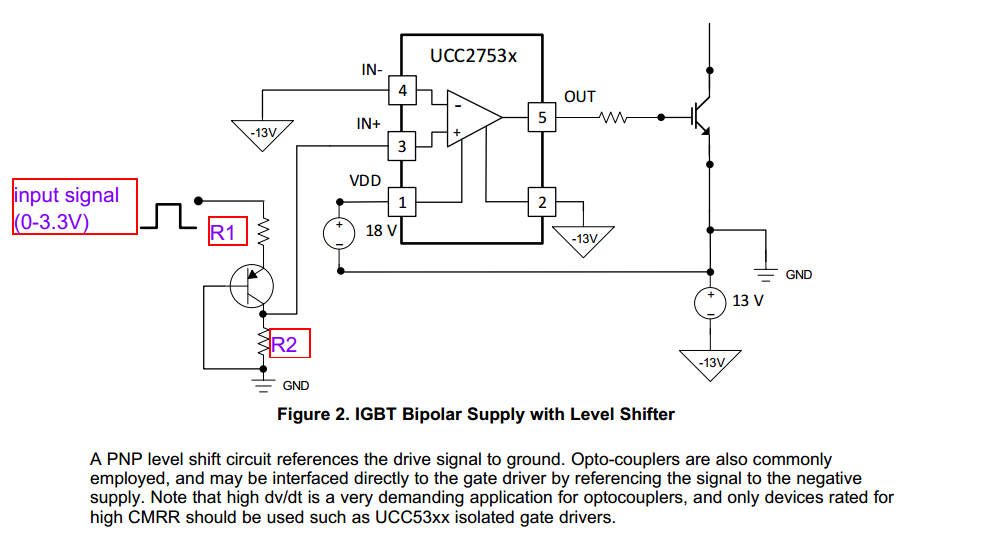

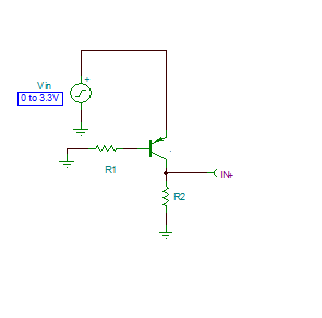

A PNP level shift circuit references the drive signal to ground is proposed in document SLUA169A, which is shown in the figure. 2.

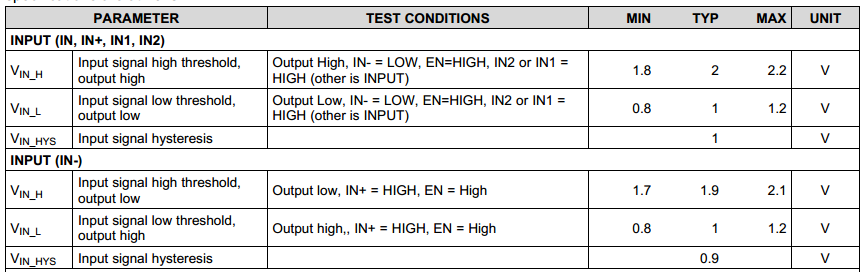

As shown in Figure2, when IN- is -13V. if IN+ voltage is higher than -11.8V (-13v+1.8v), the OUT is 18V, if the IN+voltage is lower than than -12.2V (-13v+0.8v), the OUT is -13V. the selection of 1.8V and 0.8V is based on the datasheet of ucc2753x, as shown in the following figure.

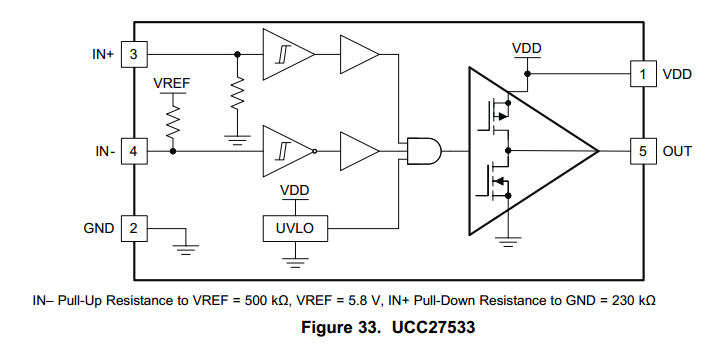

The IN+ is pulled down to -13V with a 230kΩ resistor as shown in Figure 33. if the input signal is 0V. the R2 can be calculated with formula R2>230kΩ*(12.2/0.8)=3.5MΩ.

Has anyone evaluated the speed of the PNP level shift circuit, as shown in Figure 2?

if the speed is ns level, can anyone recommend a high speed pnp transistor?

If the speed is low, Is there any other level shift circuit from TTL to negative negative voltage that can improve the speed between the input signal signal and the ucc2753x?