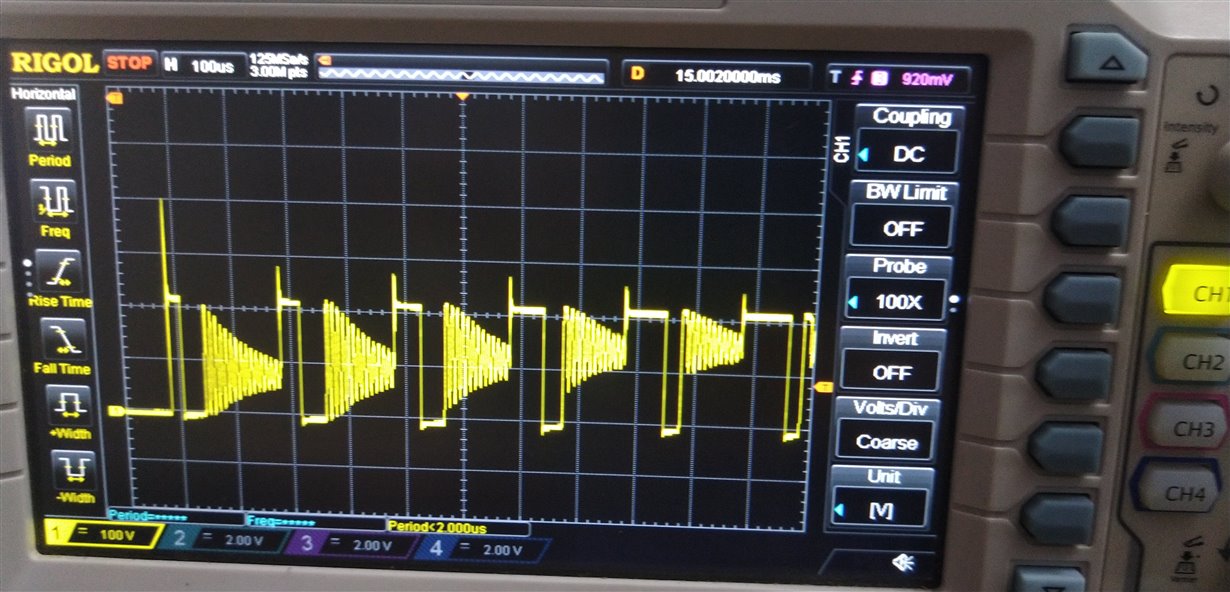

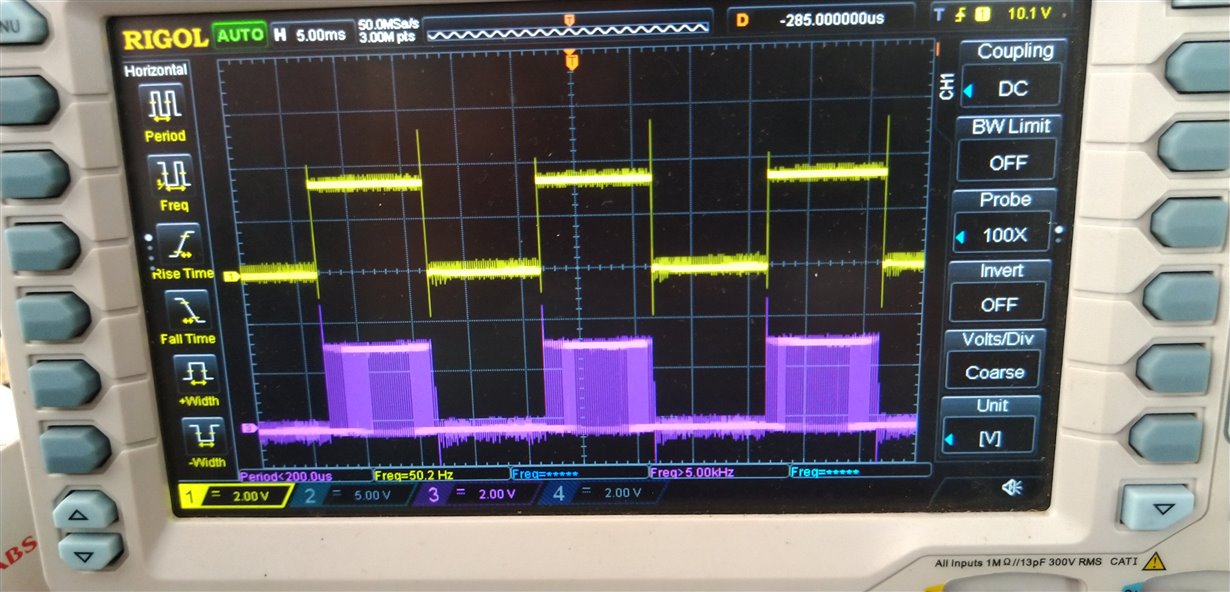

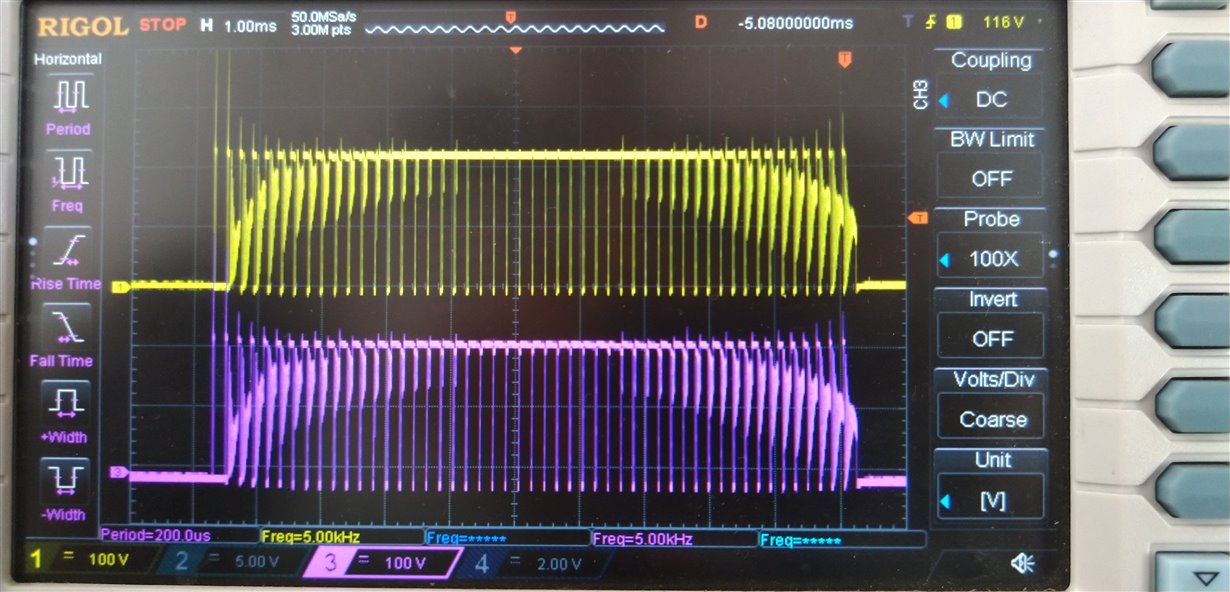

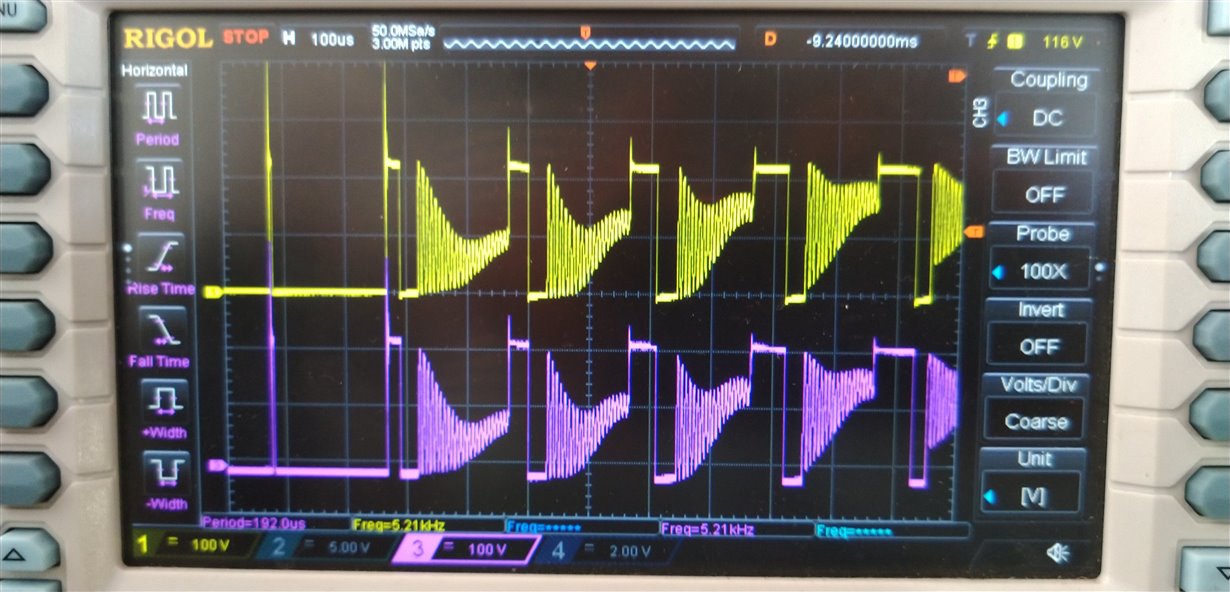

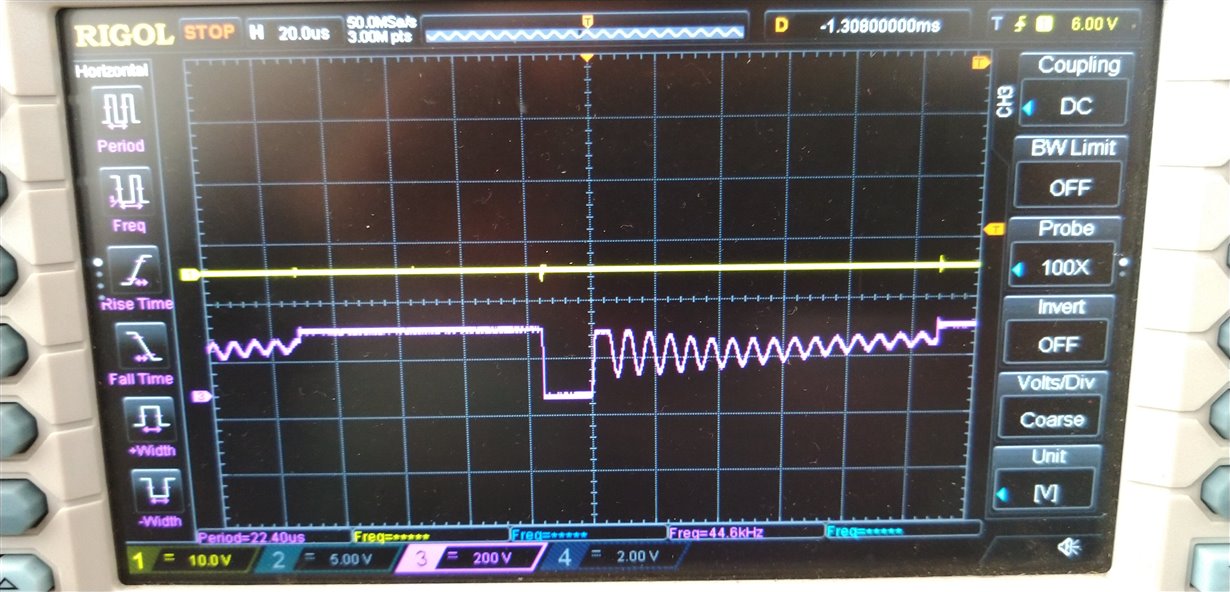

Hai i am designing a 1.65kw solar inverter.i have h-bridge in the output side for 50 Hz ac generation.i am using IGBT STGW20NC60VD AND ARE DRIVEN BY UCC27712DR for ac generation.I have applied spwm with 90 percent duty cycle in the high side and simply square pulses on the low side for ac generation.I found the ringing and peaks as shown in the image in the gate signal which are causing the mosfets to be too hot when high loads are applied at the end of the h-bridge.What could be the possible reason behind this issue?

The image shows signals ,when the gates of the IGBT were probed.