One customer is designing UCC28070 on 2.3kW (390V / 5.9A) function.

※Input is 200Vac

But problem is occurring, Vds ringing is large.

My question is two points below, please let me know any advice;

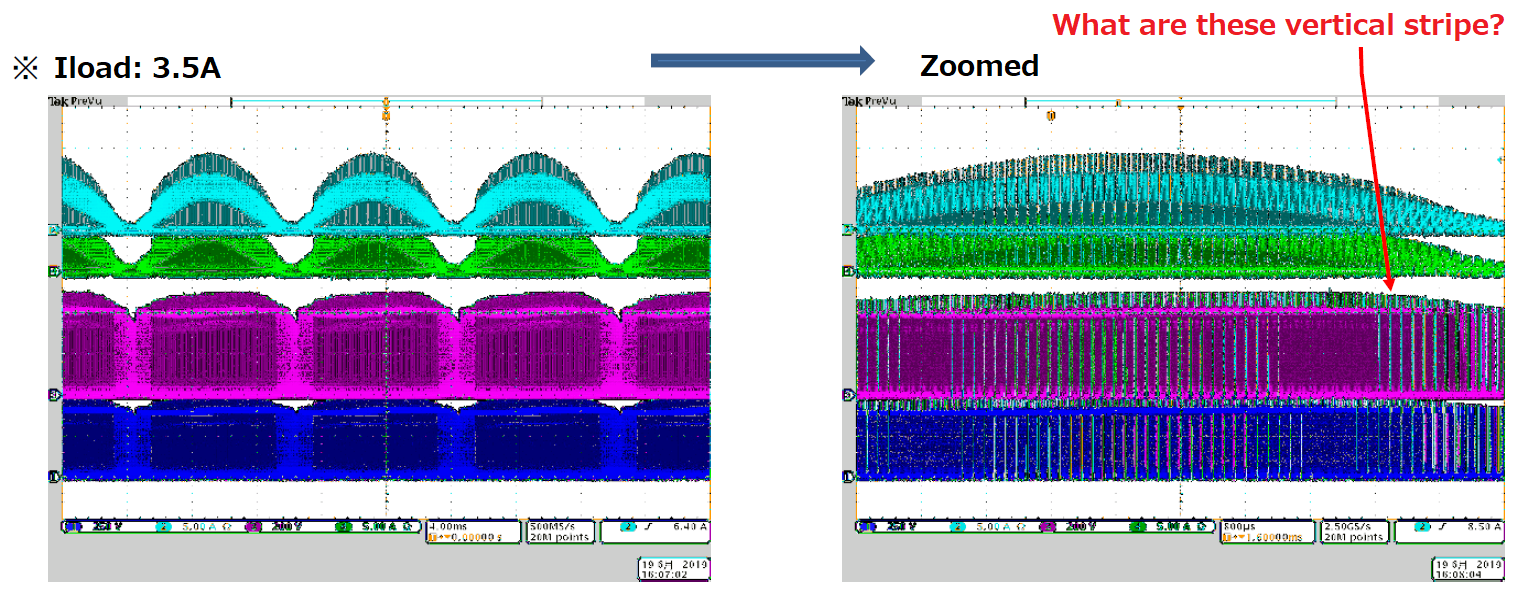

①When load current increase to "0A → 0.5A → 1A → --- → 5.9A" and measure by oscilloscope, waveform is conspicuous vertical stripe.

What is the reason of below vertical stripe?

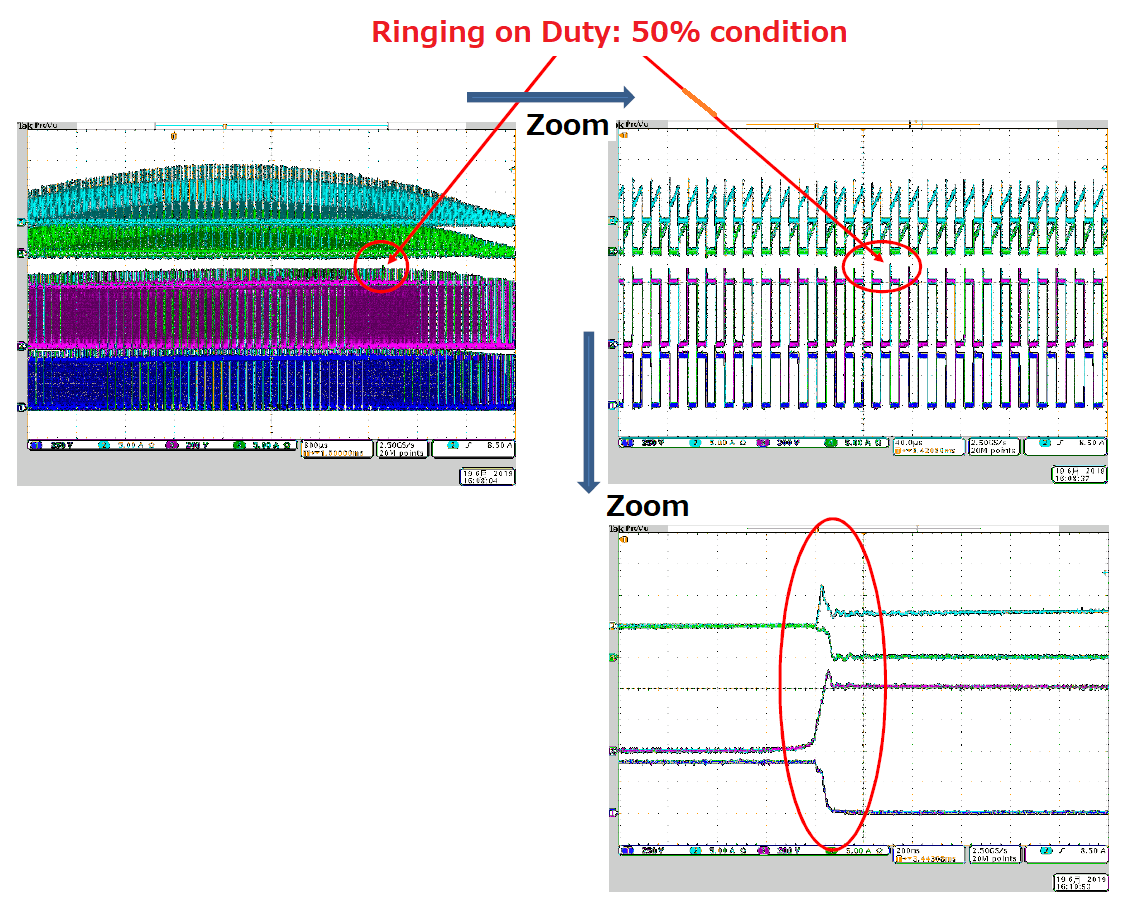

②When timing for duty cycle exceed 50% (Less than 50% → 50%), large VDS ringing is occur and larger current become more large VDS ringing.

※In the case of "over 50% → less than 50%" is no problem.

Please let me know about the reason of increase VDS ringing by over 50% duty.

And, is there any idea for reduce ringing?

Best regards,

Satoshi