Hi all,

Refer this thread for design details:

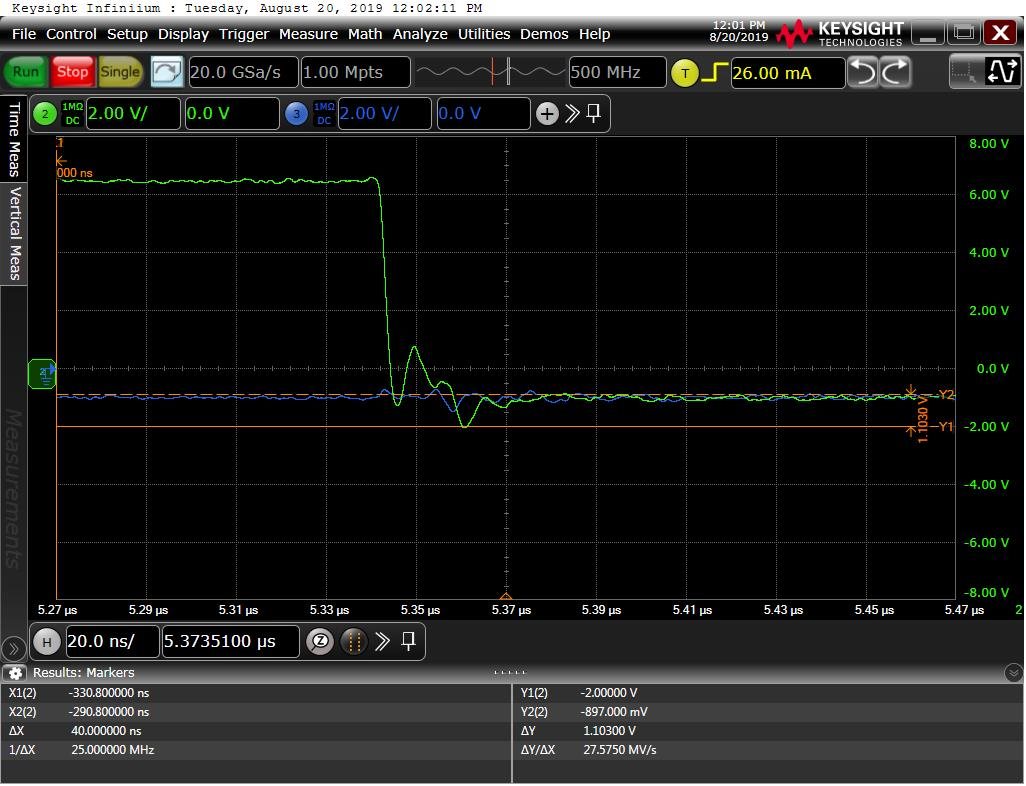

Recently we are seeing the failure in gate driver IC UCC21520.

Failure condition: OUTB to VSSB impedance short.

What would be the reason for above failure condition?

The module is worked for a month and after that failed during start up itself.

Refer attachment for schematics.Expecting your valuable reply.

WIth regards,

P.Selvam.GAN driver section.pdf