Hello everyone,

I have a problem with a boost converter based on the 2PH EVM and hope somebody could help me find the cause.

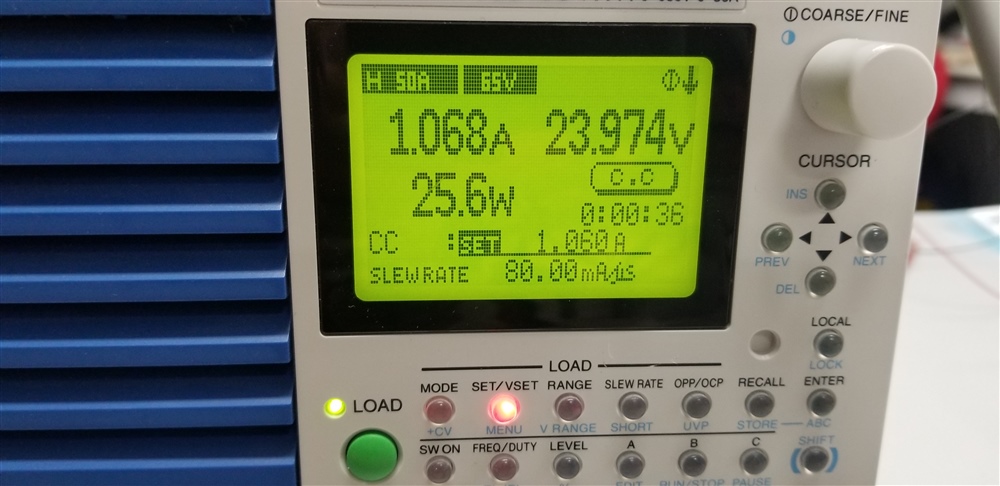

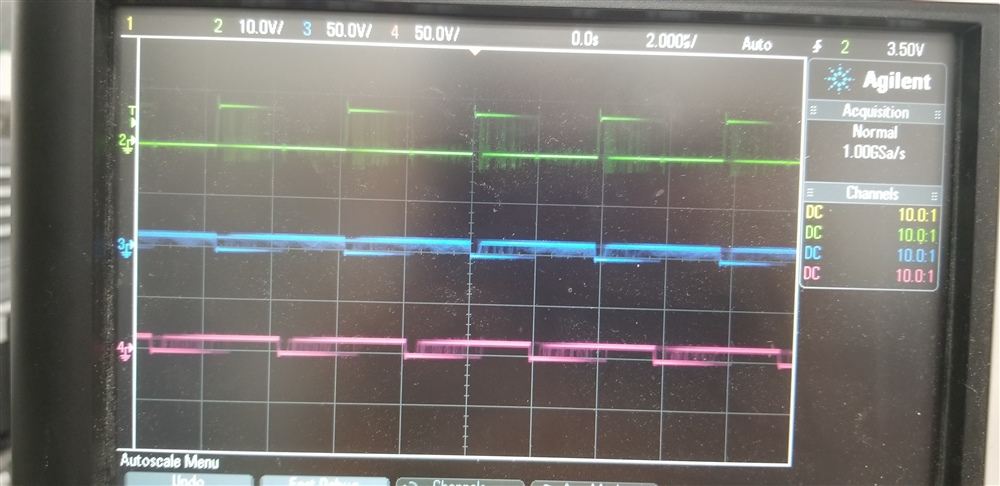

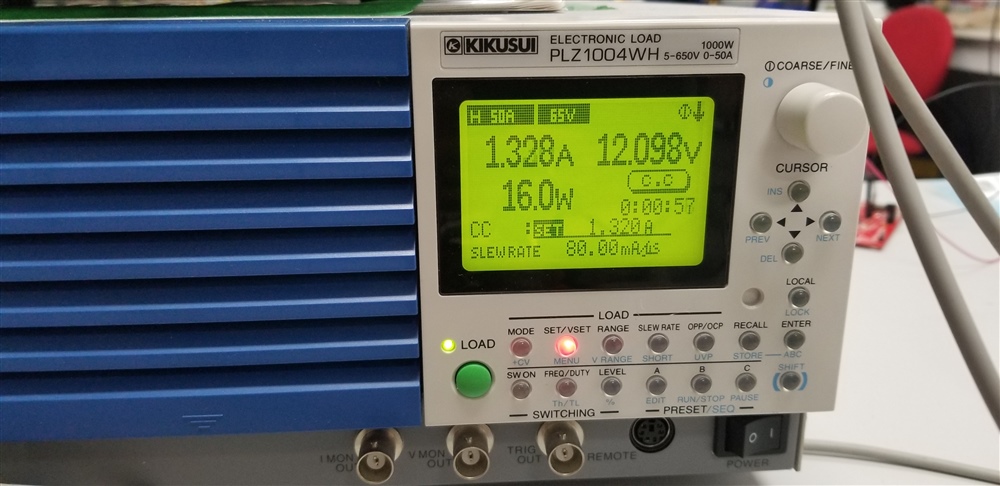

The converter works properly up to about ~1A at 24V. When I go over that current, I will hear a noise and suddenly voltage drops to about10 to15V. It also happened in lower currents as well. It seems to be very random!

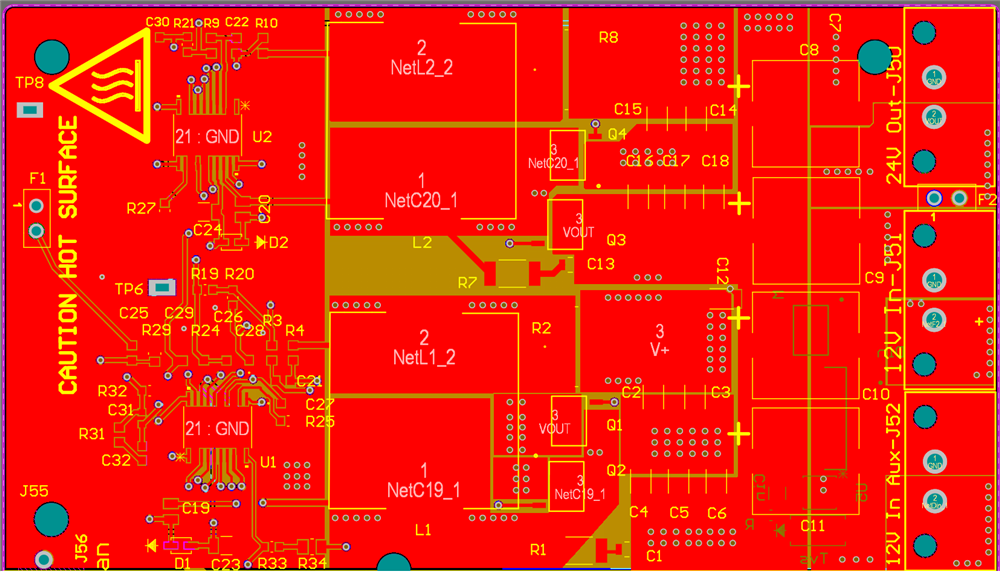

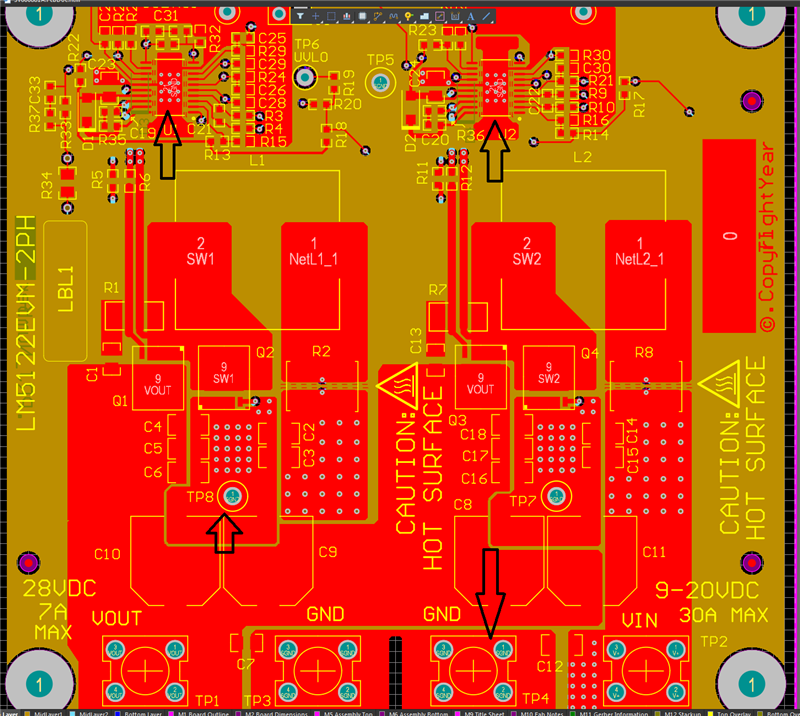

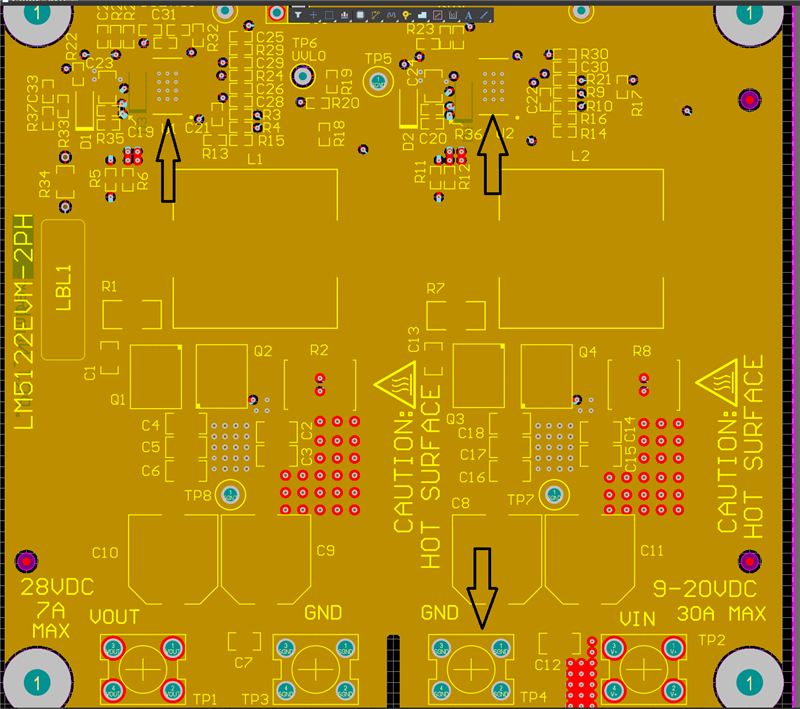

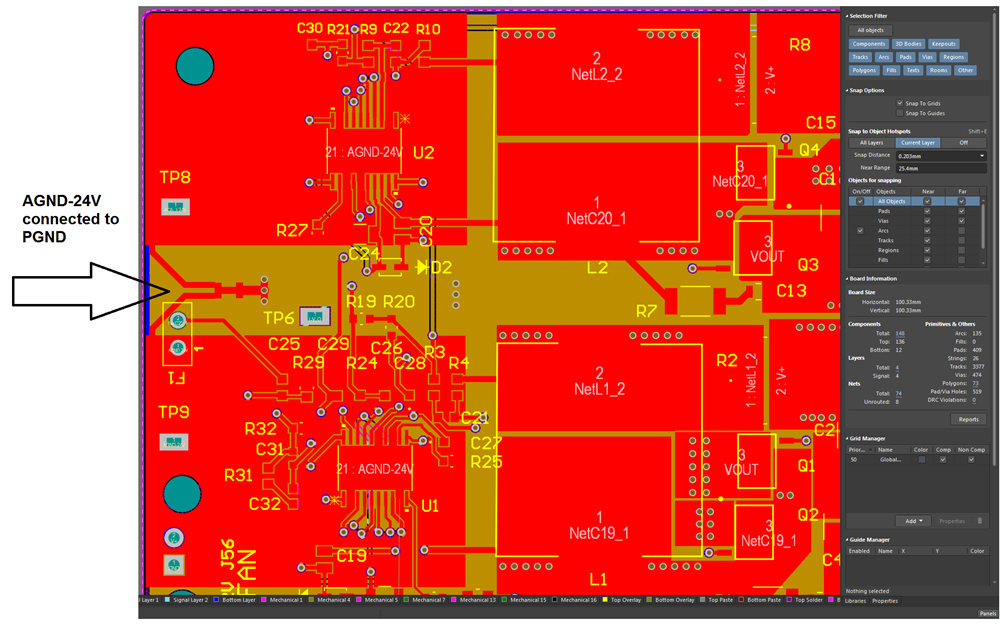

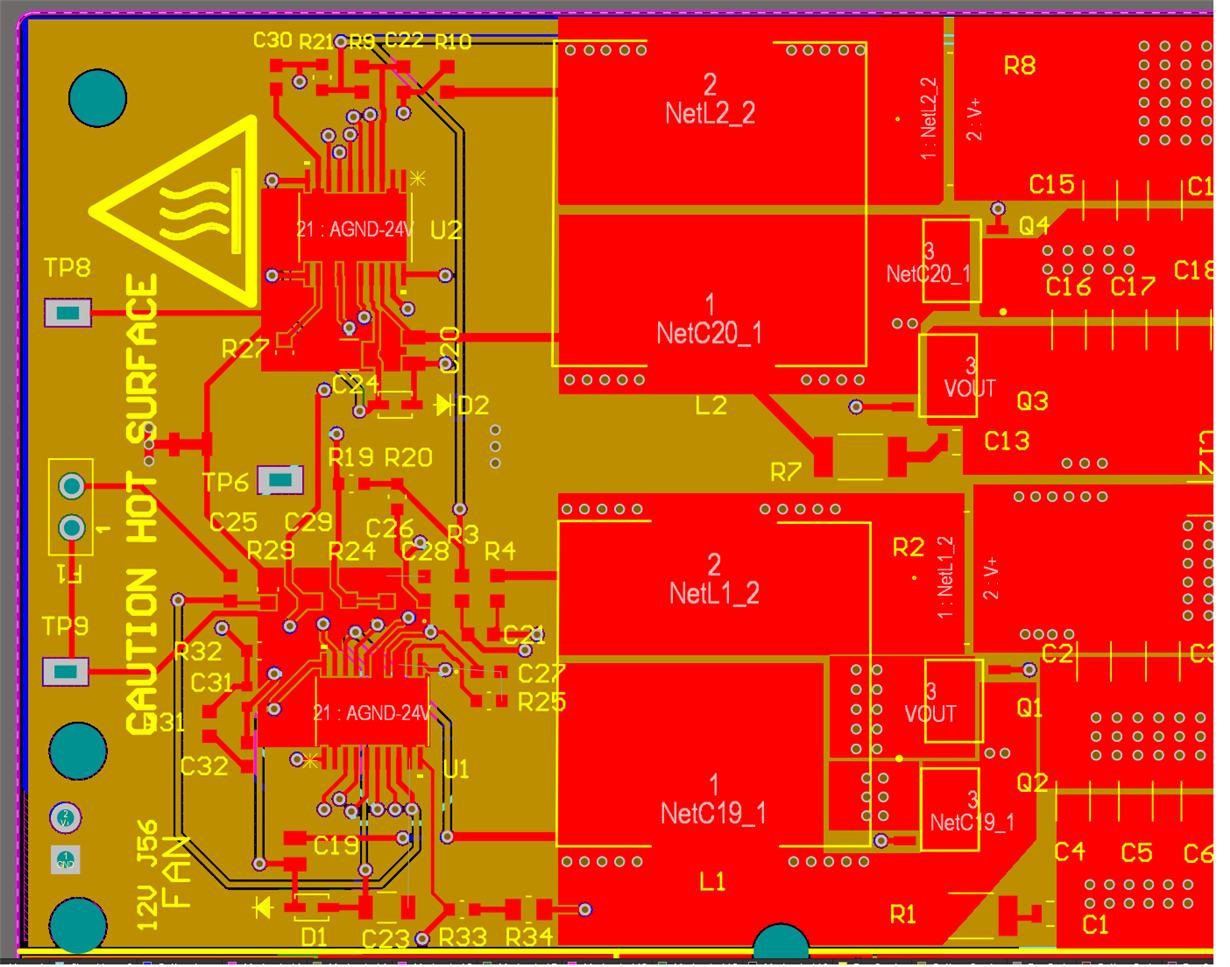

I read the forum and notice that it is mentioned PGND ANDAGND should be separated. In my 4layer PCB, they are not separated as it was not mentioned in schematic (see attached picture).

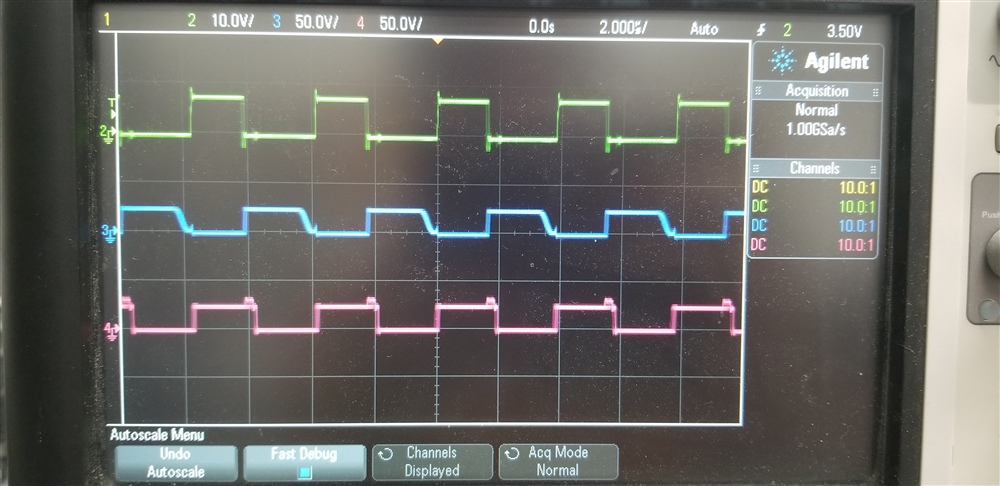

My layout has been made based on the LM5122EVM-2PH. I have checked my gate signals and they are clean as crystal! I don't know where the problem can be!? any idea?