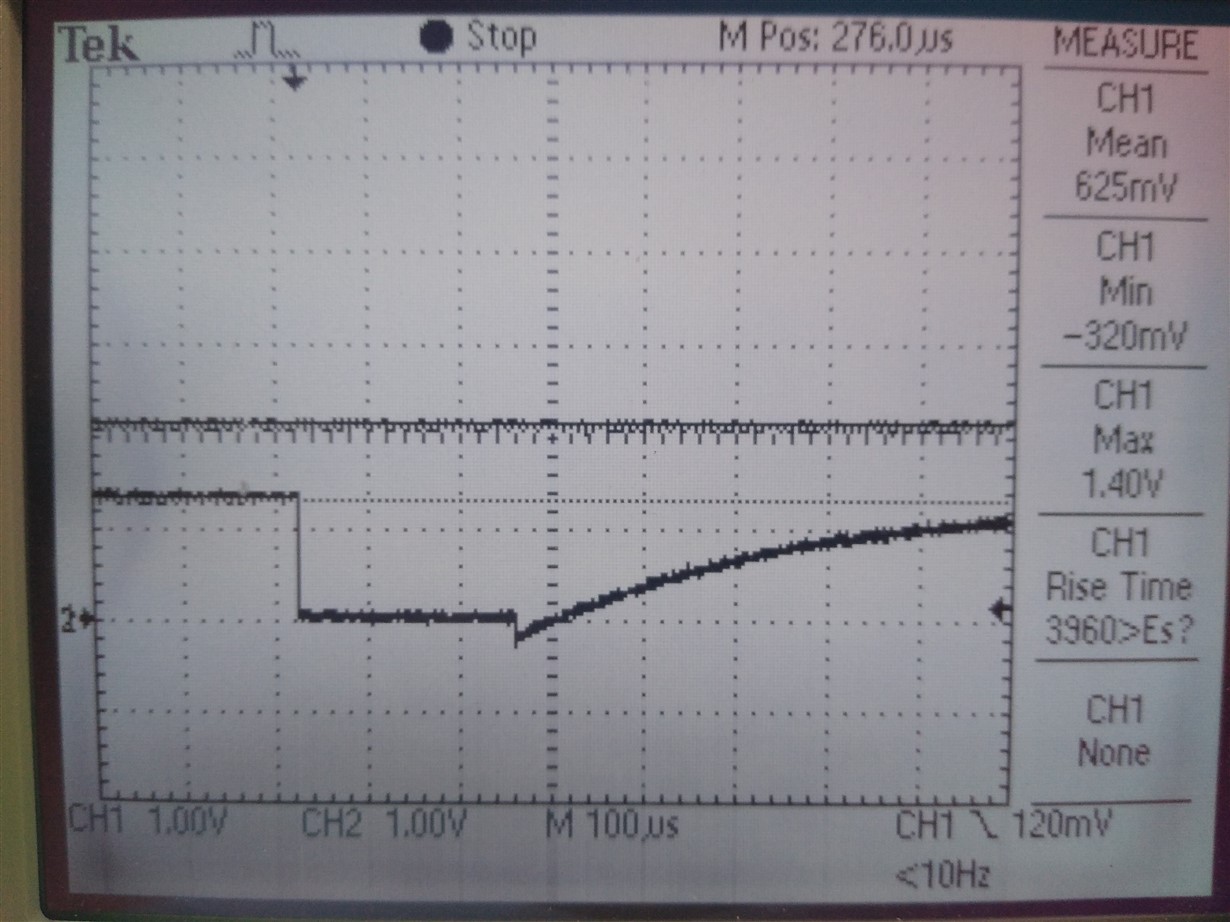

I found an issue on this forum that seems to describe a problem we are having with the TPS63020 locking up in a shutdown state:  . We have a battery powered design that is recharged from a solar cell. The output voltage from the TPS63020 is set for 3.35V and it includes a 0.5F supercap. Some parts have a very wide operational voltage range (down to 1.8V), so to save power we disable the TPS63020 by default and only turn it on when needed. In some cases we can run off the supercap for hours before re-enabling the TPS63020. We have the EN pin tied high through a pullup resistor but then are using an NMOS transistor with a path to ground to disable the TPS63020. We suspect that either the high switching speed or other power/ground plane transitions are causing the EN pin to bounce to a negative voltage and cause the lockup. We haven't been able to measure to confirm; every time we attach a test probe to the EN pin everything works fine.

. We have a battery powered design that is recharged from a solar cell. The output voltage from the TPS63020 is set for 3.35V and it includes a 0.5F supercap. Some parts have a very wide operational voltage range (down to 1.8V), so to save power we disable the TPS63020 by default and only turn it on when needed. In some cases we can run off the supercap for hours before re-enabling the TPS63020. We have the EN pin tied high through a pullup resistor but then are using an NMOS transistor with a path to ground to disable the TPS63020. We suspect that either the high switching speed or other power/ground plane transitions are causing the EN pin to bounce to a negative voltage and cause the lockup. We haven't been able to measure to confirm; every time we attach a test probe to the EN pin everything works fine.

Assuming this is the case, do you have suggestions on how to reduce possible signal bounce on the EN input? I don't want to post schematics or PCB layout in the forum posts, but I can private message someone from TI and share this information.

Thanks,

Bryan