Hello,

I am facing one issue please go through it.

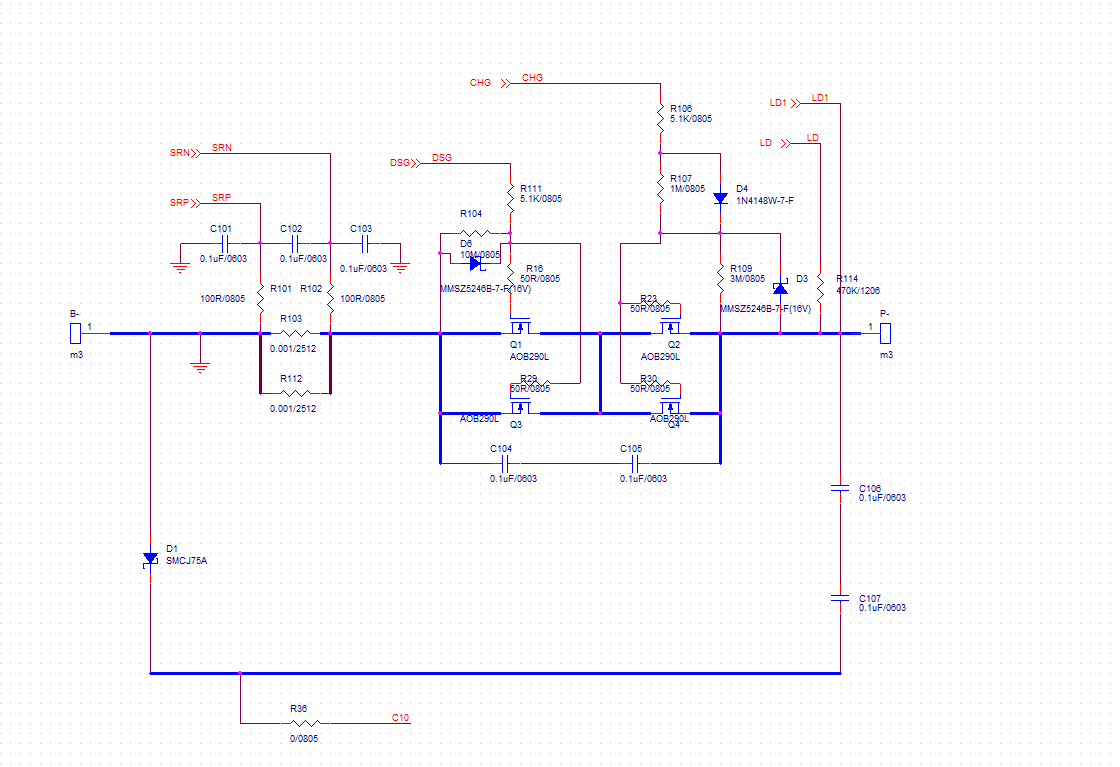

Schematic is attached please collect,

Whenever there is deep discharge and any cell voltage goes below under-voltage limit DSG MOSFET turns off. and battery voltage appears across the drain to source of DSG MOSFET.

But according to datasheet CHG MOSFET should remain On with respect to P- terminal, But voltage between gate and source of CHG Mosfet is zero. But there is a voltage of 12V between the gate of CHG Mosfet and B- terminal .

.

What may be the reason.