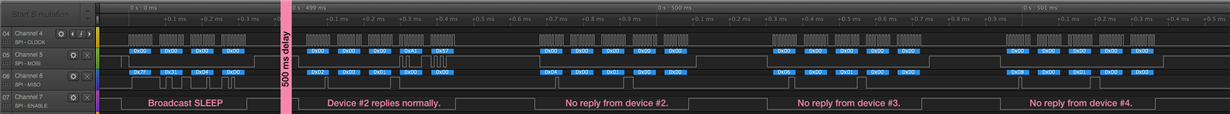

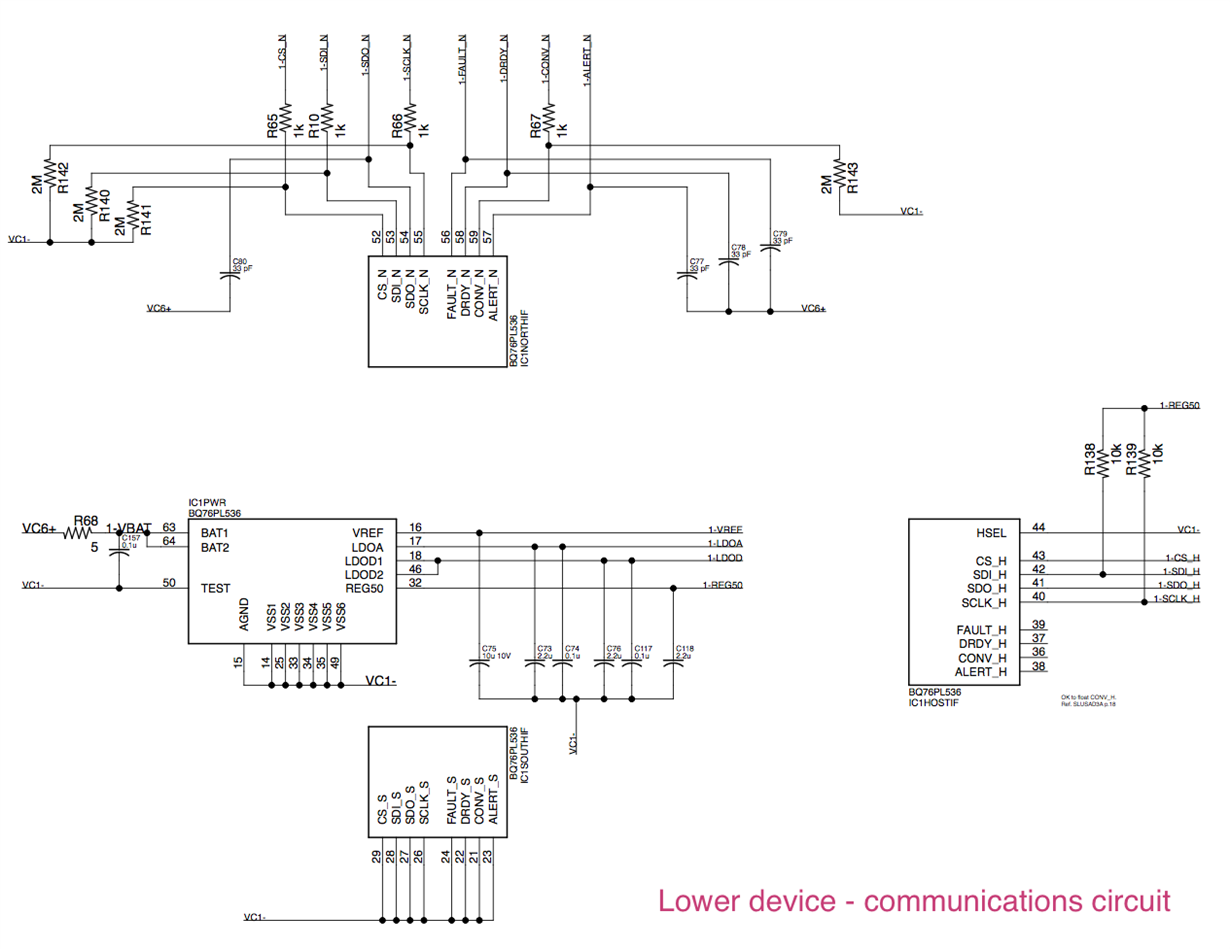

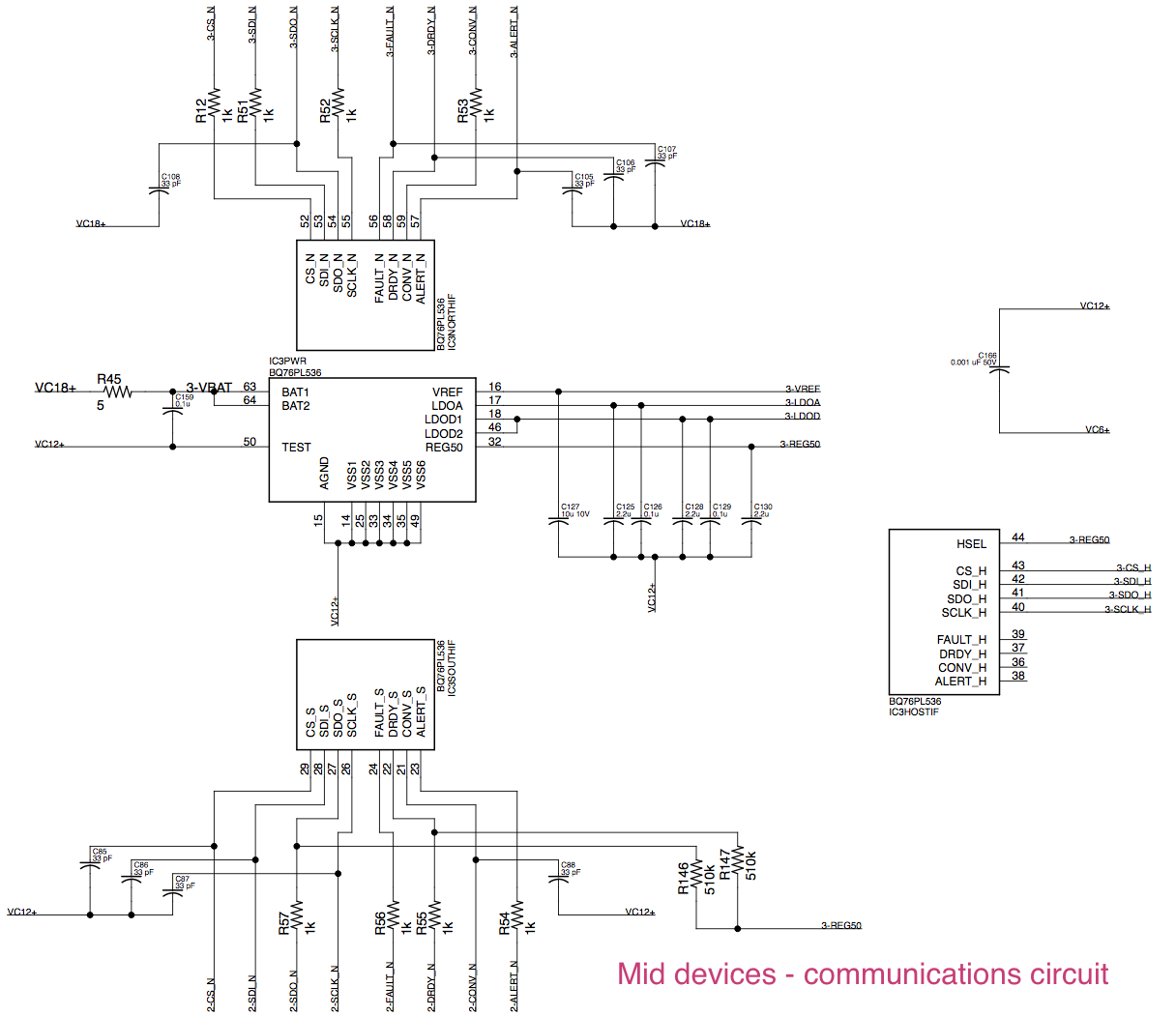

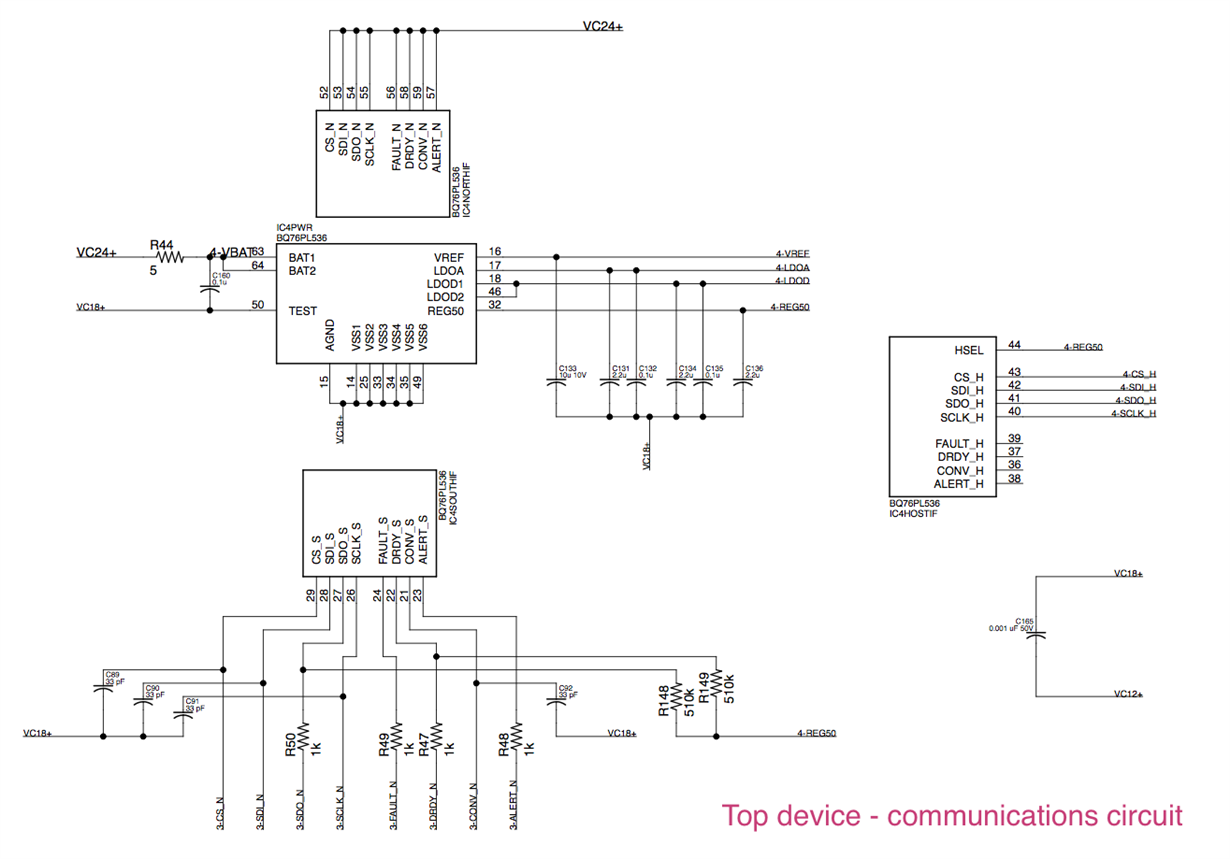

We are having a communication issue with a PCB based on the BQ76PL536A. A short time after the stack is put in SLEEP mode, the upper three devices stop replying to SPI communications. The system consists of four BQ76PL536A devices controlled by a C2000 host processor. A reproducible test case is included. The system properly discovers, configures, and measures all the BQs. However I am unable to communicate with all but the first BQ in the stack after putting them into sleep mode, this includes bringing the BQs out of sleep mode. Below is a log of the communications between the C2000 and BQ stack. The first test has a long delay (0.5 seconds) after the sleep command which causes all but the first BQ to not respond to a read. The second test is the same except with a shorter delay (10 ms) in this case all BQs still respond. The only action taken before the following communications is the discovery process that addresses the BQs. The devices have not been flashed with custom OTP configuration. Before each test, power is cycled to the BQ devices. After devices #2-4 stop replying, issuing a stack reset (7F 3C A5 57) and re-addressing the stack does not cause the upper devices to respond. The only way to re-establish communications with these devices seems to be removing and re-applying power to them. // Test 1 Time [s] MOSI MISO 0 0x00 0x7F // Broadcast Sleep 8.50833E-05 0x00 0x31 0.000170167 0x00 0x04 0.00025525 0x00 0xD0 //~0.5 second delay 0.499042833 0x00 0x02 // Read device #1 DEVICE_STATUS register. 0.499127917 0x00 0x00 0.499213 0x00 0x01 0.499298 0xA1 0x00 // Device #1 responds normally. 0.499383083 0x57 0x00 0.499680833 0x00 0x04 // Read device #2 DEVICE_STATUS register. 0.499765917 0x00 0x00 0.499851 0x00 0x01 0.499936 0x00 0x00 // No reply from device #2. 0.500021083 0x00 0x00 0.500318833 0x00 0x06 // Read device #3 DEVICE_STATUS register. 0.500403917 0x00 0x00 0.500488917 0x00 0x01 0.500574 0x00 0x00 // No reply. 0.500659083 0x00 0x00 0.500956833 0x00 0x08 0.501041917 0x00 0x00 0.501126917 0x00 0x01 0.501212 0x00 0x00 0.501297083 0x00 0x00 Expected behavior: devices reply normally to reads, with valid CRCs. Observed behavior: devices reply with only 0x00 (invalid CRC). Test 2 Time [s] MOSI MISO 0 0x00 0x7F // Broadcast Sleep 8.50833E-05 0x00 0x31 0.000170083 0x00 0x04 0.000255167 0x00 0xD0 // Delay ~10 ms 0.010989417 0x00 0x02 // Read device #1 DEVICE_STATUS register. 0.0110745 0x00 0x00 0.011159583 0x00 0x01 0.011244583 0xA1 0x00 // Device #1 responds normally. 0.011329667 0x57 0x00 0.011627333 0x00 0x04 // Read device #2 DEVICE_STATUS register. 0.011712417 0x00 0x00 0.0117975 0x00 0x01 0.0118825 0xA1 0x00 // Device #2 responds normally. 0.011967583 0x23 0x00 0.012265333 0x00 0x06 0.012350333 0x00 0x00 0.012435417 0x00 0x01 0.0125205 0xA1 0x00 0.0126055 0x0F 0x00 0.01290325 0x00 0x08 0.012988333 0x00 0x00 0.013073333 0x00 0x01 0.013158417 0xA1 0x00 0.0132435 0xCB 0x00 //

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.