Hi,

1) Can BQ76930 supports less than 6 cells ? If yes, what would be the cell connections for 5 and 4 cell series configuration.

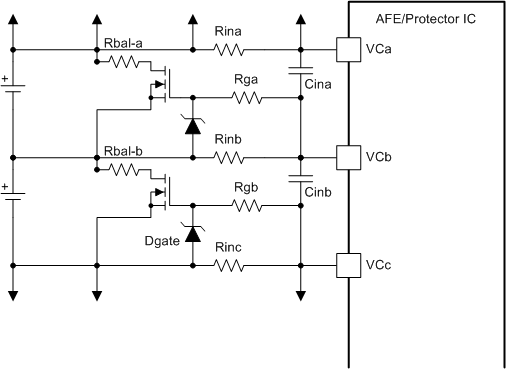

2)The BQ76930 EVM shows usage of PFET in external cell balancing circuit. Is BQ76930 supports NFET in external cell balancing and let us know the connections.

Regards,

Vasanth M