Hello,

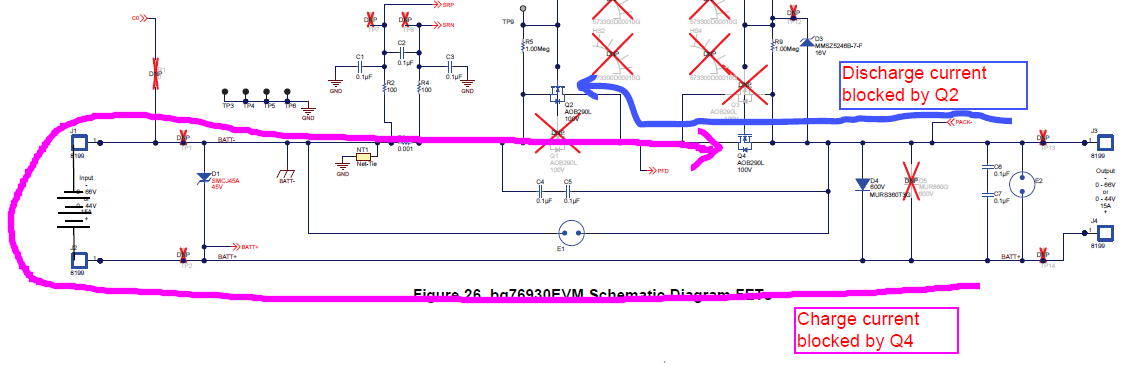

I am brand new to the TI battery chipsets, and have been looking at schematic for the BQ76930EVM. I'm having trouble understanding how the charge and discharge FETs are meant to operate. To my way of thinking the charge FET should be activated when you want to apply a charge from an external power source to charge the batteries, and the discharge FET would be activated when you want to control the output of the battery driving a load. When I look at the configuration on the schematic (Page 44 of SLVU925B) it looks as though both the discharge (for Q2) and the charge (for Q4) FETs would need to be activated to have current flow from J1 to J3. I do see the "PFD" node in the middle that creates an alternate path (through Q17) to J3 using the "pre-charge" control, but it still requires Q2 to be activated. I'm not sure how you would integrate a charge system into this configuration? Does this mean that for most operations both charge and discharge need to be active at the same time (or discharge in combination with pre-charge). Any help would be much appreciated. Thanks in advance.

Dan.