Hi,

we have severe problems while refreshing the registers of the BQ78Z100 via I2C. We observed that the BQ frequently stops charging/discharging by deactivating both of its FETs. The effect first seems to be randomly happening, but we managed to produce an environment which can reproduce the error:

System Configuration

- BQ78Z100EVM (alternative our own Battery Module based on the BQ78Z100EVM)

- MCU connected to the BQ I2C interface (I2C running at 100 kHz)

- 2x 450 mAh LiPo cells connected to the BQ78Z100EVM

- 8.5 V power supply connected to PACK+ / PACK - on EVM board for charging

- Test SW on the MCU which runs only a single test applicatoion:

const uint32_t TestDly = 250;

void getGaugeStatus () {

int16_t voltage = 0;

int16_t current=0;

int16_t remaining=0;

int16_t full=0;

int16_t soc=0;

I2CRegRead (BQ_I2C_SLAVEADDRESS, VOLT, 2, (uint8_t *) &voltage);

delayUs(TestDly);

I2CRegRead (BQ_I2C_SLAVEADDRESS, INSTCURR, 2, (uint8_t *) ¤t);

delayUs(TestDly);

I2CRegRead (BQ_I2C_SLAVEADDRESS, RM, 2, (uint8_t *) &remaining);

delayUs(TestDly);

I2CRegRead (BQ_I2C_SLAVEADDRESS, FCC, 2, (uint8_t *) &full);

delayUs(TestDly);

I2CRegRead (BQ_I2C_SLAVEADDRESS, SOC, 2, (uint8_t *) &soc);

delayUs(TestDly);

return;

}

void chargeBatteryTest () {

deactivateDsgFET ();

deactivateChgFET ();

for (int i=0; i< 100; i++) {

getGaugeStatus ();

}

activateDsgFET ();

activateChgFET ();

for (int i=0; i< 100; i++) {

getGaugeStatus ();

}

while (1) {

getGaugeStatus ();

delayUs(TestDly);

uint32_t safetyStatus = readStatusReg(SAFETY_STATUS);

delayUs(TestDly);

uint32_t safetyAlert = readStatusReg(SAFETY_ALERT);

delayUs(TestDly);

uint32_t pfStatus = readStatusReg(PF_STATUS);

delayUs(TestDly);

uint32_t pfAlert = readStatusReg(PF_ALERT);

delayUs(TestDly);

while( (safetyStatus != 0) && (safetyAlert != 0) && (pfStatus != 0) && (pfAlert != 0) ) {

getGaugeStatus();

}

}

}

Test Procedure

- Power supply off

- Start MCU

- read BQ status registers

- activate charge/discharge FETs

- continuously read the BQ status registers via I2C

- Wait ~ 30 seconds ==> OK

- no errors occured

- read status registers works fine

- battery voltage present @ PACK+/PACK- contacts due to active FETs --> OK

- Activate Power supply providing 8.5 V 200 mA charge supply

- Wait 1 - 10 seconds ==> ERROR

Error Behavior

- After the above testing procedure the BQ does not respond on the I2C bus anymore

- no action on SDA lane (neither ACK nor data transfer): SDA lane stays high due to pull-up whenever BQ has SDA control

- no attempt to hold SCL lane low to throttle bus speed

- non responding BQ may appear at any stage

- within transfering a read byte from BQ to MCU

- after a successful completion of a read/write bus transfer

- while writing the register address to the BQ

- BQ deactivates the charge & discharge FETs

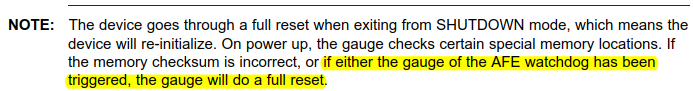

- After a certain time (not further evaluated at this point) the BQ continous to respond normally to any I2C requests

- The charge & discharge FETs stay disabled

- The FETs can be re-activated via I2C again

Error Analysis

- Increasing the delay (TestDly) between 2 consecutive I2C register reads reduces the probability of this error

- When I run the Test with the Battery Management Studio & the EV2300 adapter I could not reproduce the error (but I noticed a delay of ~14ms between 2 reads)

- However I have not found any hint in any datasheet about any delay requirements except the "bus free time between stop and start" of 1.3 us (which we do meet of course)

- The error was never observed when no charging current was provided

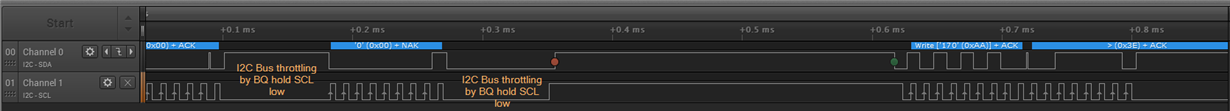

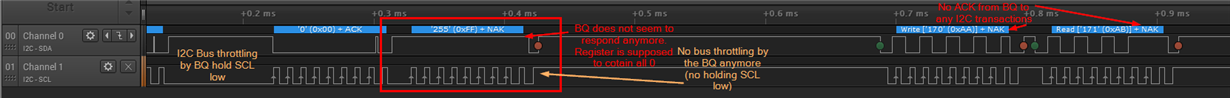

- I have captured the activity on the I2C bus during the error:

- I personally have the following theory:

My collegue Philipp Schmidbauer already has asked for a service request at your stand at the Electronica in Munich 2 weeks ago, but never received any answer.

I would highly appreciate any help on this topic as it is a absolut kill criteria for our application, i.e. you can't build a UPS which accidently resets itself and thus turning the full system off. That's not what I would commonly call a "uninterruptable power supply"!