Hi,

I have several questions about the UCD9244 configuration when aiming for an external synchronisation :

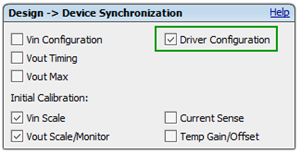

We would like to know if the FUSION setup we chose is correct :

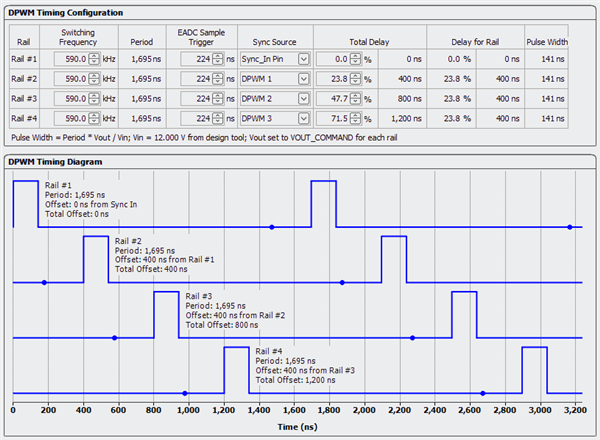

- All 4 PWM engines are by default defined to run at 590 KHZ.

- The signal applied to SYNC pin is a 625KHz clock because we want finally to run at 625 KHz.

- We want all 4 PWM engines to be synchronized by the external 625KHz clock.

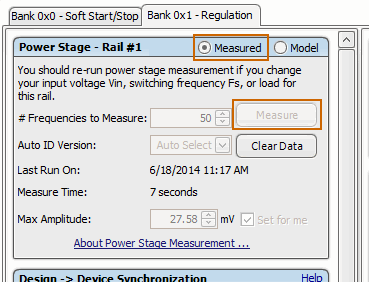

The FUSION setup is the following :

- EADC was set to 423ns according to the formula.

QUESTIONS :

1) Is it correct to keep all the 4 "switching frequency" at 590KHz ? or should we define only rail1 at 590Khz and Rails2,3,4 at 625 KHz ?

2) Is it correct to change only the EADC for rail 1, and keep the EADC of rails2,3,4 to the initial 224 ns value, or should we change EADC for all the 4 rails ?

MEASUREMENTS :

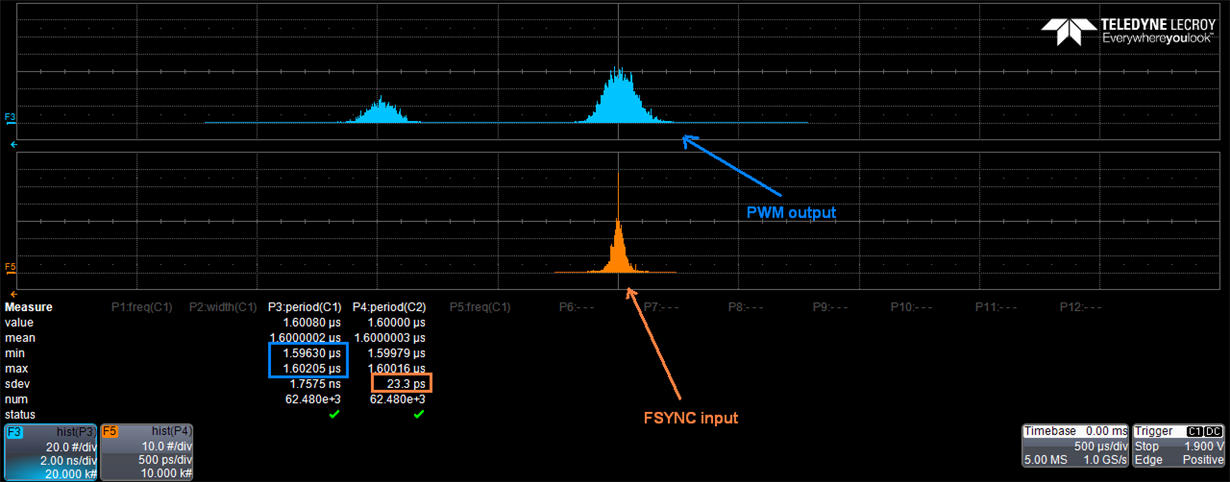

3) When looking at the PWM output I noticed that the PWM period was not constant although the input is very stable :

These 2 graphs are histograms of the measured period.

the 625Khz period exists (1.6ns) but also another discret distant from 4 ns.

==> Is this "normal" ? might this result from an inadequat FUSION setup ?

PRINCIPLE:

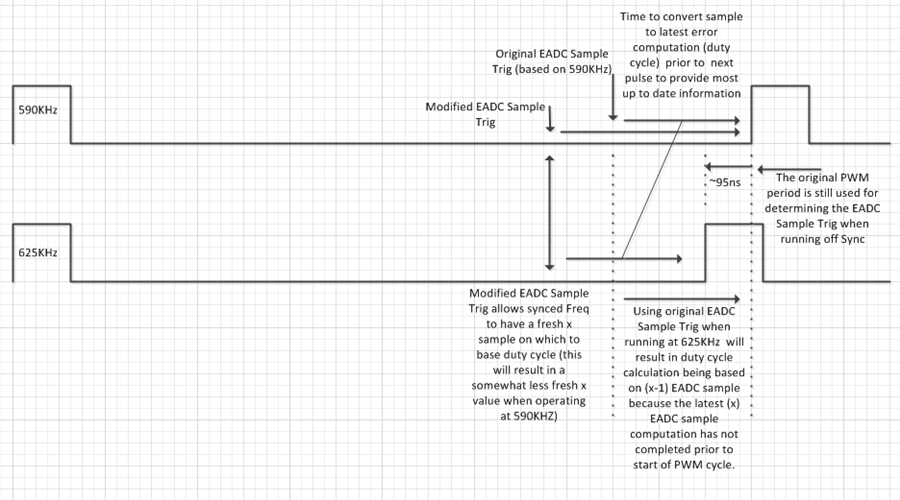

The default switching frequency was defined at 590 KHz. And therefore the CLA bank coeff calculated by FUSION are based upon this asumption.

However the effective switching rate applied is 625KHz, meaning that finaly the PWM is running at 625KHz with coeff valid for 590 KHz.

If we want the correct coeff to be applied, then we have to specify the Fsw freq to be 625Khz.

BUT in this case it is not possible to synchronize with the external signal since it MUST have a higher frequency.

Is there way to work around this problem ? May be by using 2 different projects ?

Thank you for your support,

Best regards,

Bruno