Hi,

I run into a problem and found out, that the DPWM generates too short pulses.

Yes, I know, there were settings to prevent this, but unfortunately it fails. Is this a known issue?

Here my test setup.

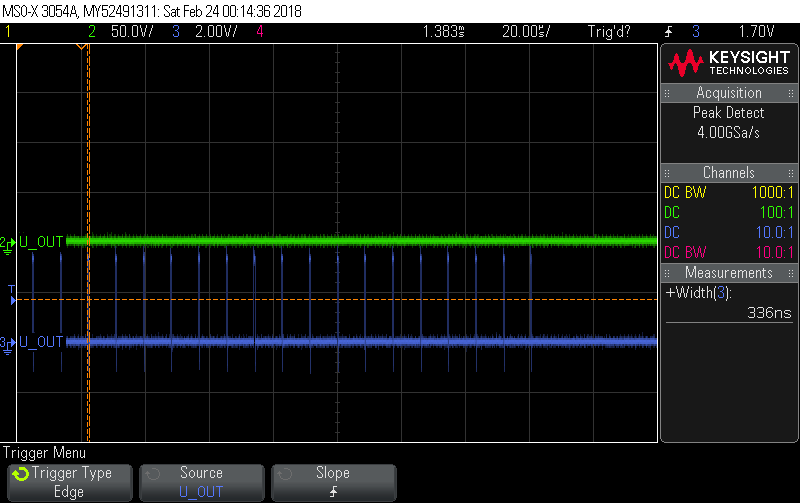

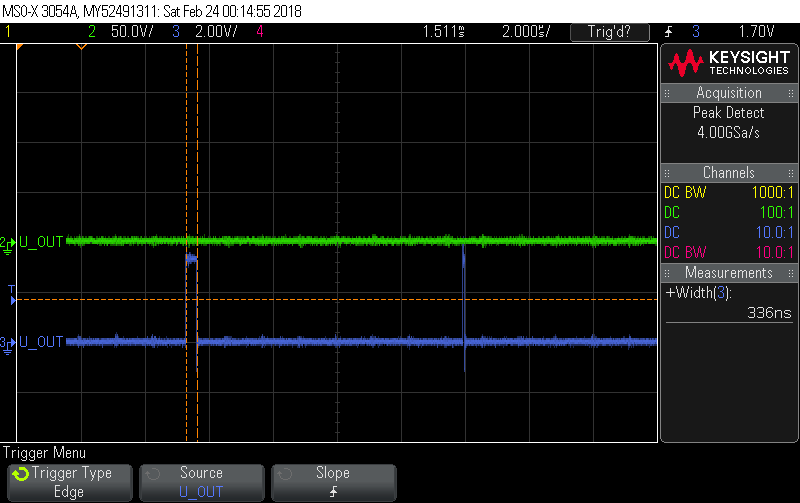

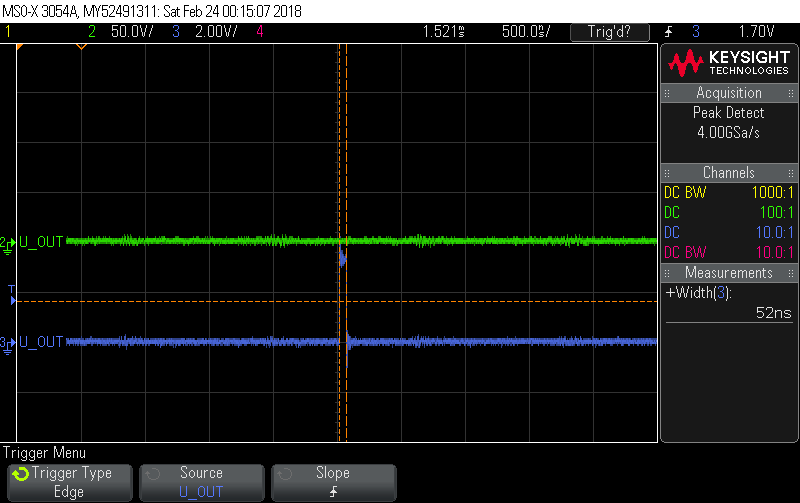

I config my three DPWMs (three Phase System) to get the duty cycle from the filter section. The filter section is set up to get the input from the CPU. When I set the filter input to 1 manually the output runs up until the max. possible pulse width (here 3.3µs) is reached, thats ok. When I set the value to -1 than the pulses getting smaller and smaller until no pulses were generated any more. I set Minimum Duty Mode = 1, so the minimum pulse width is determined by the value in the DPWMMINDUTYLOW register. Unfortunately I see pulses down to 30ns.

Using Minimum Duty Mode = 2 the pulses getting smaller and smaller and the system ends up by generating pulses with the minimal pulse width programmed. This works fine. So I am sure, that the value in DPWMMINDUTYLOW is correct.

Whats wrong???

With best regards

Gerhard