Other Parts Discussed in Thread: UCD7242

HI,

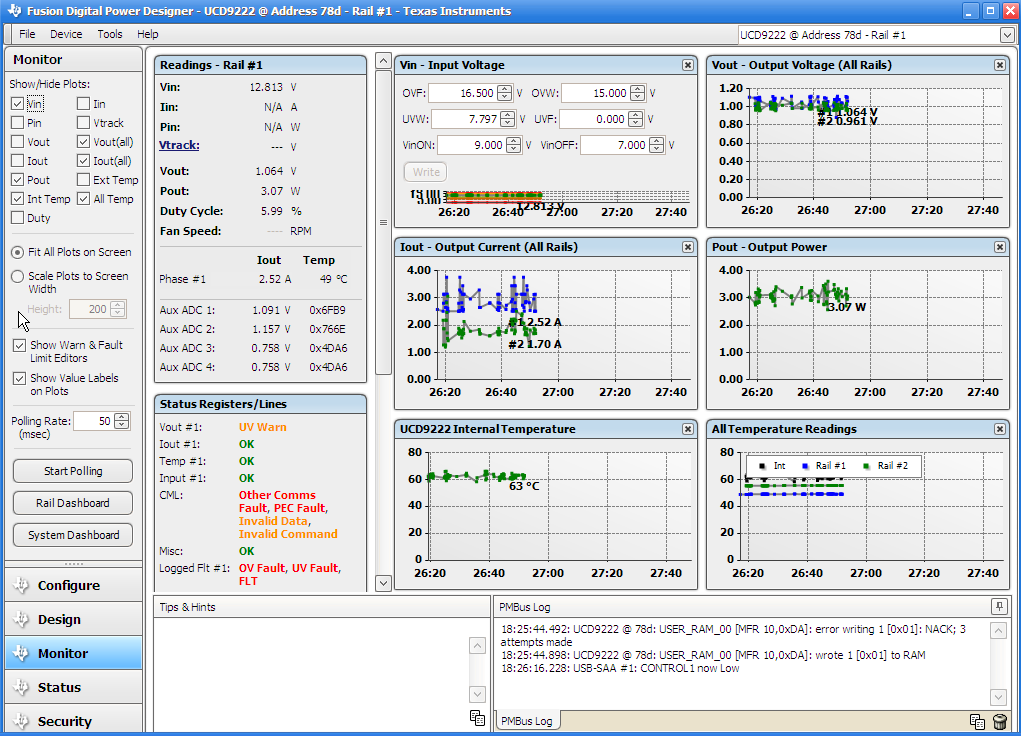

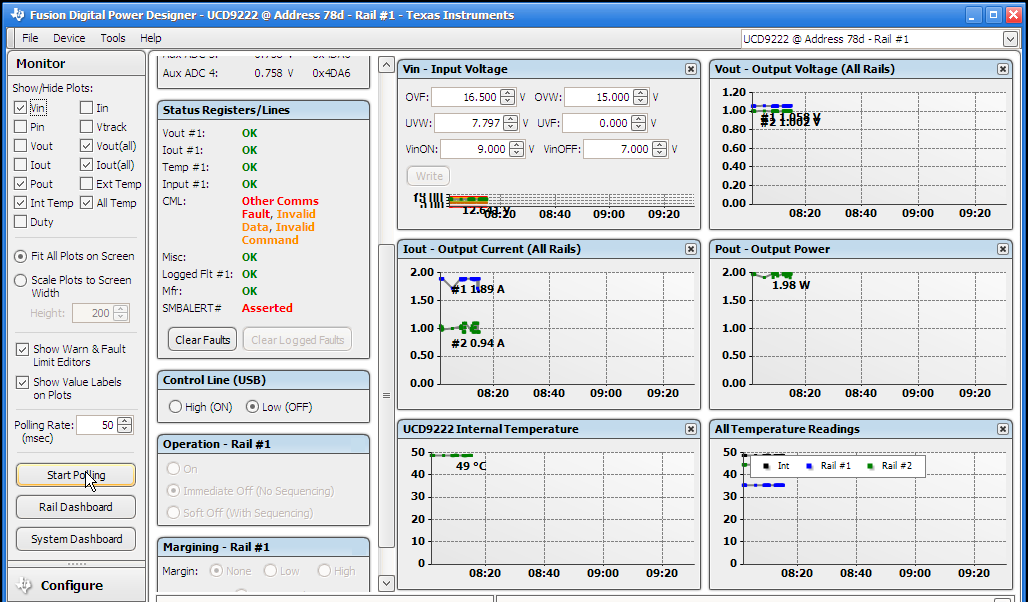

I have a board with two DSP(C6678). Each one has dedicate one UCD9222 and one UCD7242 to provide Core(rail #1: 1.1V) voltage and fix(rail #2: 1.0V) voltage.

When I enable only One DSP Core and Fix voltage, both 2 DSP UCD9222 and UCD7242 can works fine.

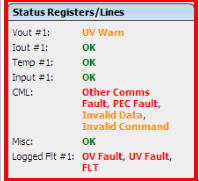

But when I enable 2 at the same time. the DSP2 UCD9222 and UCD7242 will trig FLT and reset, and retry then reset again. Same FPGA Code with DSP1 and DSP2 pin assignment exchanged, the failure one is still DSP2.

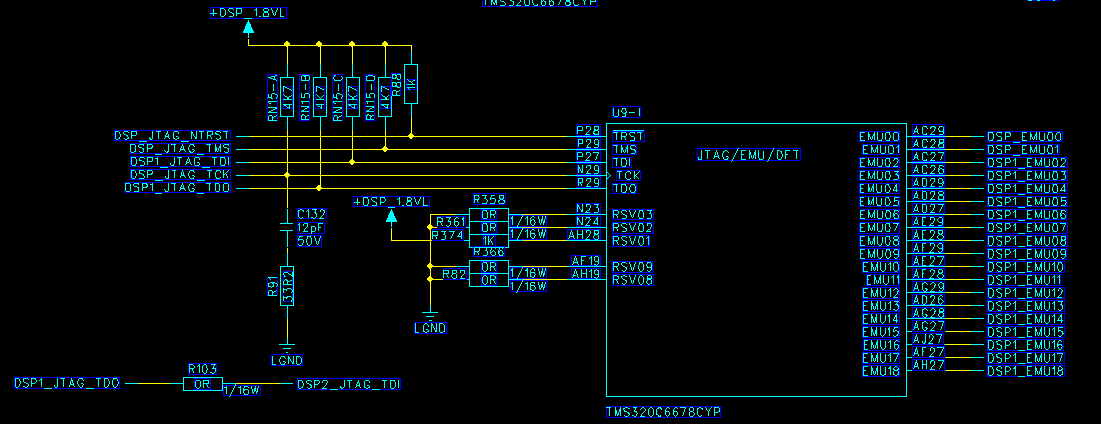

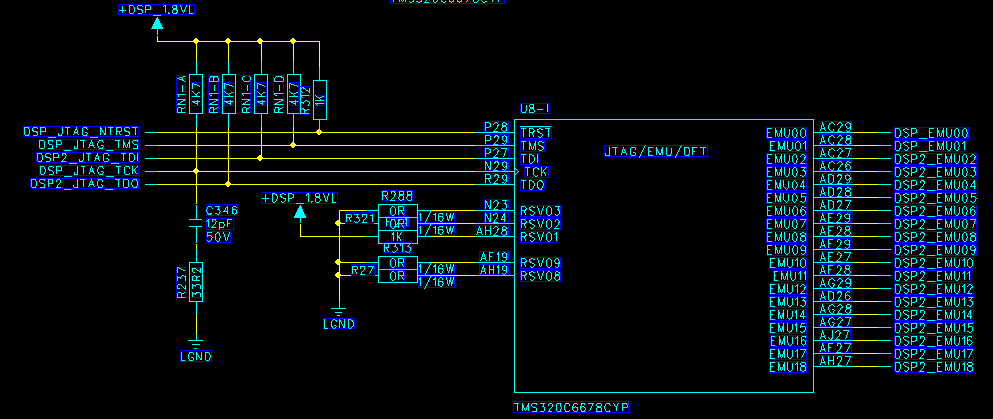

The only connection between 2 DSP is the JTAG chain(one JTAG connect, daisy chain 2 DSP) as below:

Any possible that cause such symptom? Please help.

Thanks a lot.