Tool/software: Code Composer Studio

Hello, I was recently learning the UCD3138HSFBEVM_029 demo board .

I met a serious problem.

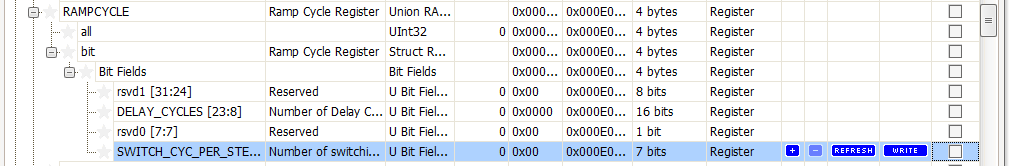

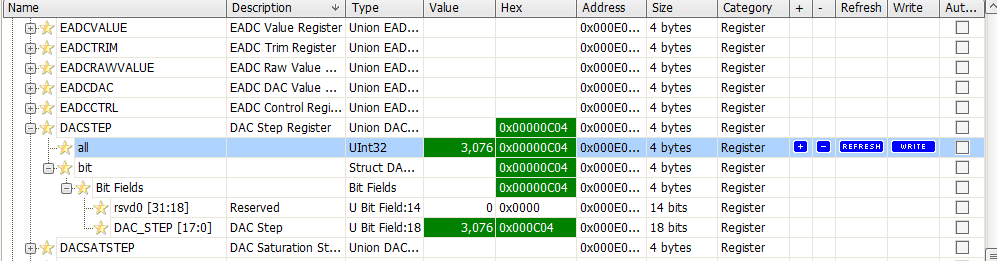

Now,I am calculating this time of ramp up for HSFB UCD3138,but after modified the SWITCH_CYC_PER_STEP,the time of ramp up for HSFB UCD3138 dosn't change.

Why?Please give an answer, thank you。