Hello,

We are experiencing the below issue:

- After the chips are configured, tried to turn on the voltage rails by writing OPERATION_ON and pull pin PMBUS_CTL high. The rails remain low.

- Checking the status registers, I got:

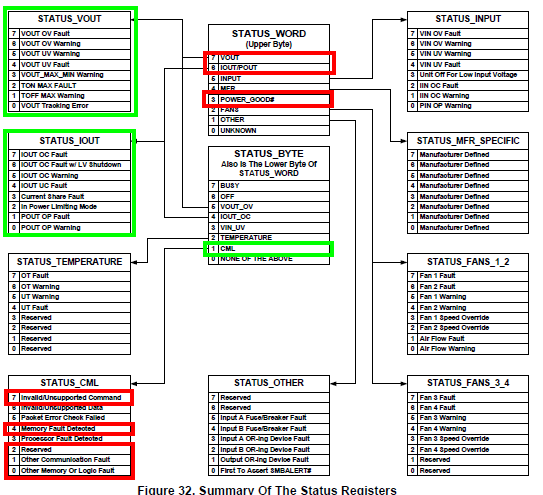

- STATUS_MFR_SPECIFIC: 0x80

- STATUS_WORD: 0x00c8

- STATUS_CML: 0x97

- Sending SOFTRESET does not help with the issue.

Could you please help me with these questions?

- Do the chips require an nRESET pulse to properly reset and start outputting?

- If not, would doing so have any negative effect?

- If a hard reset via nRESET is not viable, is there any timing constrain I need to follow to properly reset and start the chip?

Thank you,

Ryan B.