We have a design which contains a 3 rails regulated using the TPS7A4901DRB.

The input voltage is between 6 and 12 V.

The output voltages are 5.0V, 3.3V, 2.5V.

The output load on these rails is a few mA (<10mA).

We have observed on some units that the output voltage creeps up, but this can take a few hours to manifest.

Some show the 5V floating up to 6V and others the 3.3V floating up to 4.0V.

This problem is more prevalent when the input voltage is 12V.

As an experiment we increased the input to 15V and saw a dramatic reduction in the time required to observe a fault.

We also noticed that if a reduced voltage is presented on the Enable pin (originally tied to Vin, 12V) then the fault is much less likely to manifest.

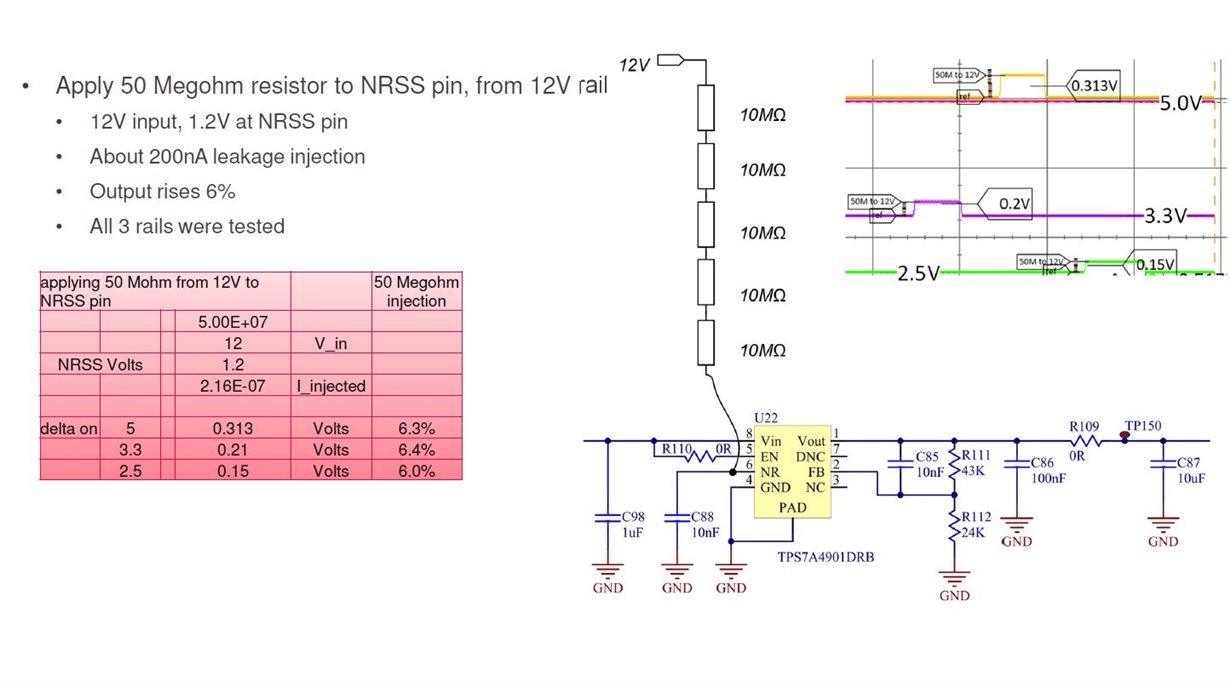

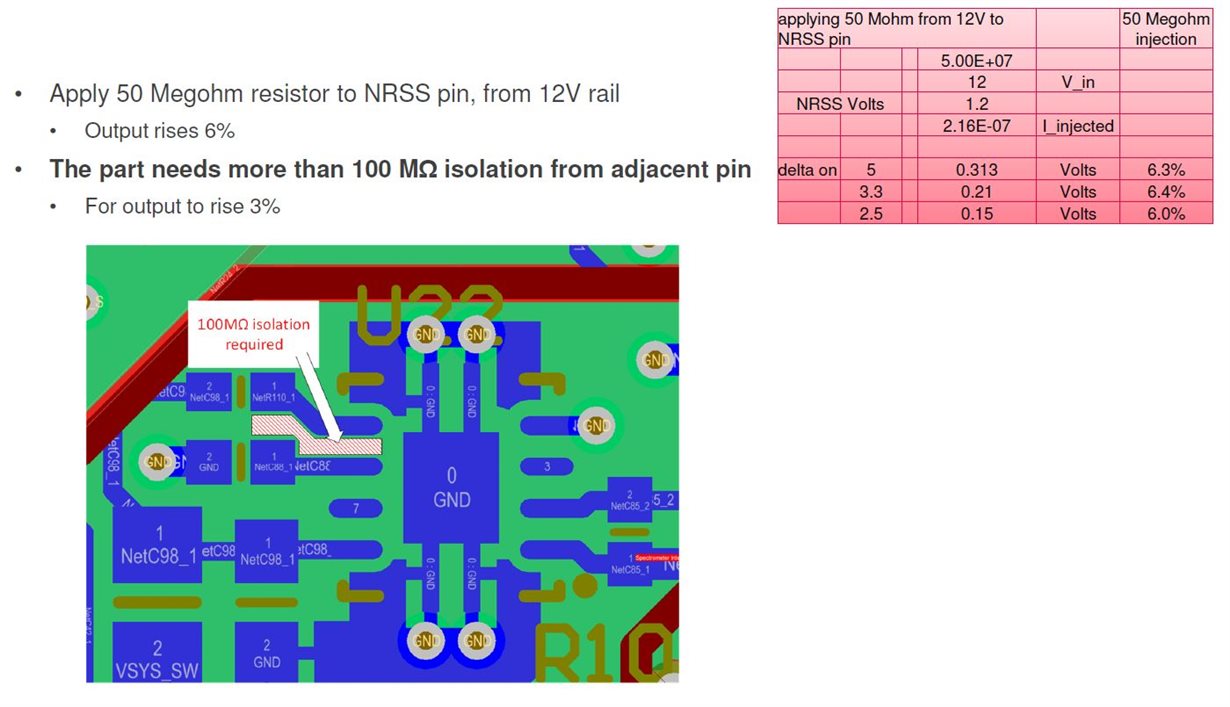

We noted a previous Ti forum thread, which mentioned a very high input impedance on this pin, and the EN pin is very close to the NR pin. Therefore as an experiment we investigated what isolation is required between the NR and EN pins by connecting the same input voltage onto the NR pin through a series of resistors as shown in the image below.

Even with a 50Meg ohm series resistance, distortion of the output voltage by 6% was observed. This implies that over 100Meg of isolation is required between these pins for correct operation.

Please could you confirm that this level of isolation is reuiqred between these pins for correct operation.