Hi,

I’d like to ask about the function of UCC28950.

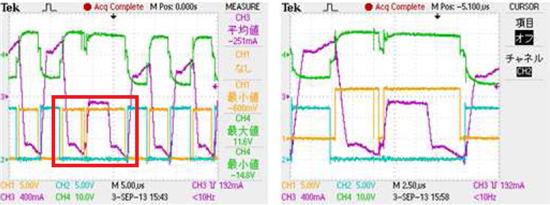

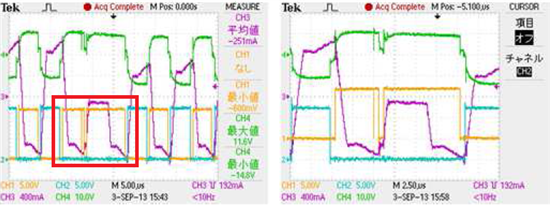

My customer evaluates load transient on his DCDC converter board, but he found some abnormal function.

He confirmed that outC/D lock up for 1 cycle after load transient(500mA→50A) regardless of outA /B waveform is normal, and he said this causes bias magnetism of transformer.

-----------------------------

-CH1:outC

-CH2:outD

-CH3:current flowing through the primary winding of power transformer

-CH4:pulse transformer(primary side)

-----------------------------

Is it probable function that outC/D lock up regardless of outA/B waveform is normal?

I think outC/D is associated with outA/B, and outC/D doesn’t lock up independently.

Could you advise me please?

I’m sorry that I can’t get schematic of the board(it is my customer’s matter).

The condition of DCDC converter board is Vin=270-280V, Vout=28V/50A.

Regards,

Yaita