Hi

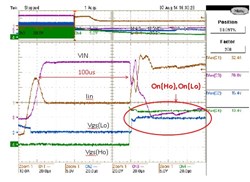

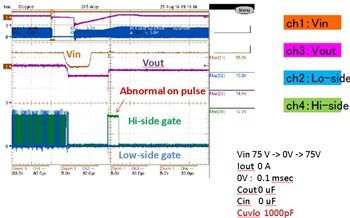

Our customer evaluate LM5035C. They tested some abnormal test then they found simultaneous on(Ho/Lo).

Could you see following photo.

They tested a short break test in the following sequence.

1.Vin=75V,Io=0A

2.shut down Vin to 0V.

3.restart Vin to 75V after 100us.

4.Turned on simultaneously occurred in the restart after 100us.

Can you any advice for this phenomenon.

And could you let me know if you have any question.

Regards,

Koji Hamamoto