Hi

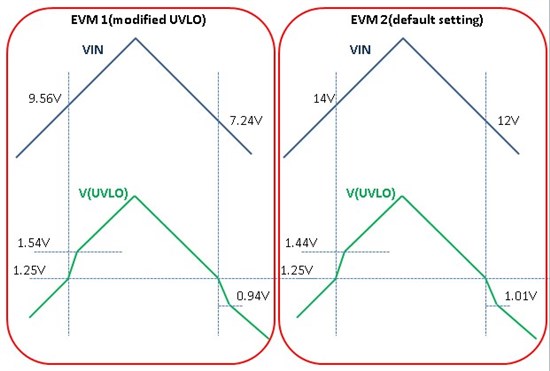

I evaluate the LM25037 EVM which is modified to lower UVLO threshold (R4 9.76kohm -> 15kohm) .

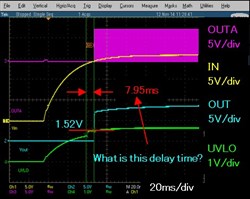

I obtained a strange behavior which is following duty cycle.

There are large changes of the duty cycle for the variation of the input voltage(Vi=11V -> Vi=10.7V).

Why does this phenomenon(large changes of duty cycle) occur?

Regards,

Koji Hamamoto