Hi

I have two question for this device.

Our customer will use this device without feedback loop at isolated push pull controller application.

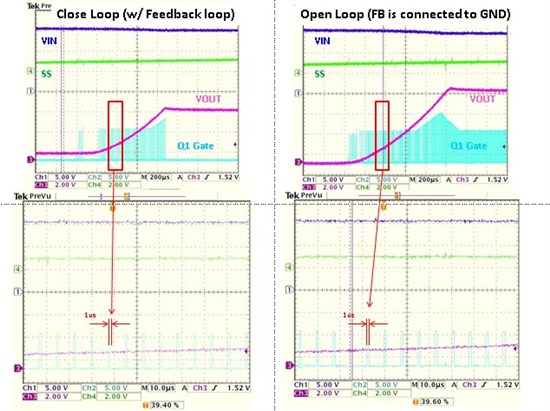

1. Dose this device have implemented soft start time when the FB pin is connected to GND?

I though this soft start operation does not work when FB pin is connected to GND. However it looks soft start operation is working during it is starting up. (It is not max duty cycle.It is narrow duty cycle such as 740ns on time.)

2. This device has delay time to start the switching operation. What time is the typical and maximum value of the delay time?

Regards,

Koji Hamamoto