Hi all,

Just a question on the bootstrap capacitor voltage drop as I am using the LM5106 datasheet, but something seems not clear.

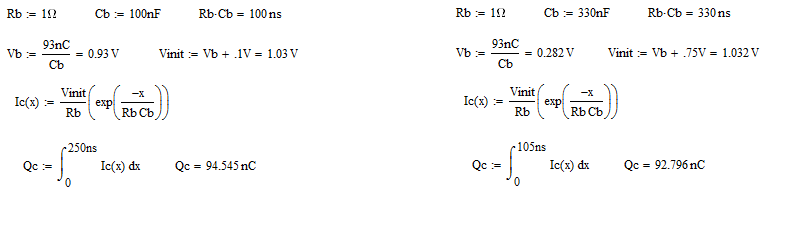

On the value for the boot capacitor for my application, I can calculate it like: Cboot=Qgtotal/VHB, being

Qgtotal = 93nC (maximum value), the total gate charge for my IPP075N15N3G MOSFET

VHB = 12V (driver dc supply) - 1V (boot diode voltage drop) - X? (X is this the mosfet Vgsmin? or what else?)

The formula in the LM5106 datasheet says that where I put X above I should use the MOSFET Vgs,min which for my switch is 4V.

However, another TI document for LM5109B-Q1, says that where I put X in the formula above I should use VHBL = VHBRmax – VHBH which are values related to the undervoltage protection.

The question is, what should I use for X in the VHB formula, and why? I am using LM5105 as gate driver.

Thanks a lot,

Leo