I have a customer asking the following questions:

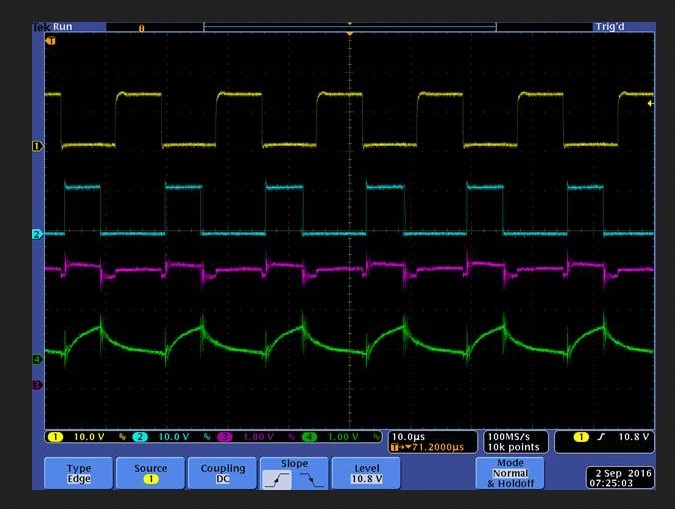

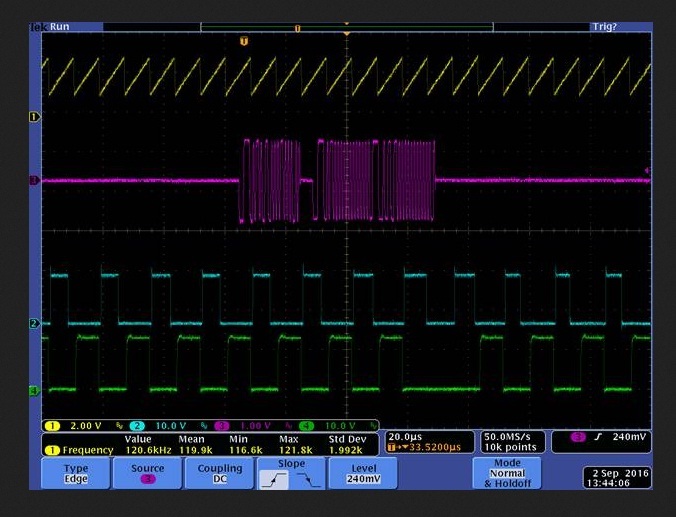

One of our suppliers utilizes a UC1846 PWB chip in their power supply design. Recently, because of tolerance stack-ups, it was realized that the dead-time for the UC1846 outputs was not of adequate duration, resulting in the power supply not regulating as expected. To increase the dead-time, the CT capacitor value was increased. The question I have is in regards to this capacitor value, and the responding dead time measurement versus the expected dead time based on the TI UC1846 datasheet. A C0402T332K5RACTU capacitor (X7R type) was installed for the CT capacitor. This is a 3300pF capacitor. Based on the formula listed in the TI UC1846 datasheet, we were expecting dead times of ~ 3300pF * 145, or ~500ns @ room temperature. Based on oscope measurements, we are seeing dead time measurements at more than twice the rate, at ~1300ns. Do you happen to know why this is occurring?

They are using X7R caps that are the proper voltage that have pretty tight specifications in terms of % etc. Is it normal that the dead time values would not follow the calculation? The oscillator frequency is fine. It is just the dead time that seems to be giving them problems in terms of calculating the proper value.

Can we help in this situation or is this the tolerance of the parts?

Thanks for your help with this!

Richard Elmquist