Background:

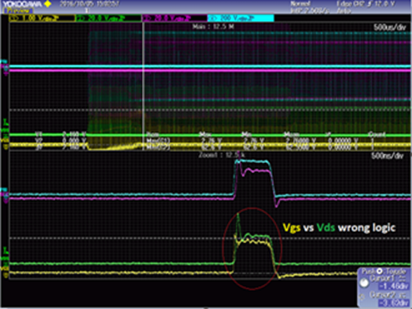

UCC27424 is presently driving SRs in a center tapped secondary application. During startup (1st 500uS), we noticed the VCC of UCC27424 was still zero volts, but the output pins were going to 2.1~2.4V. This might be due to miller effect of the switching drain of the SRs.

Ch1: SR Vgs

Ch2: SR Vds

Ch3: Secondary Winding

Ch4: Primary Winding

Questions:

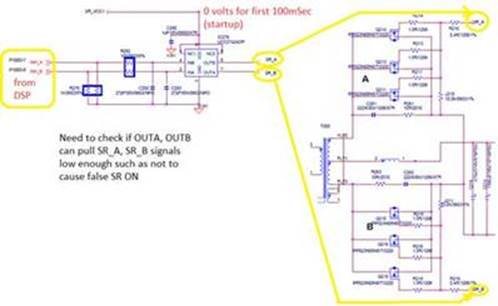

1. When Vcc is 0V, what is impedance between UCC27424 output pins (OUTA/OUTB) and Ground?

2. Will there be reliability concern on the UCC27424 if 2.1 volts difference between output pin and Vcc.

Reference data: Application circuit