Dear All,

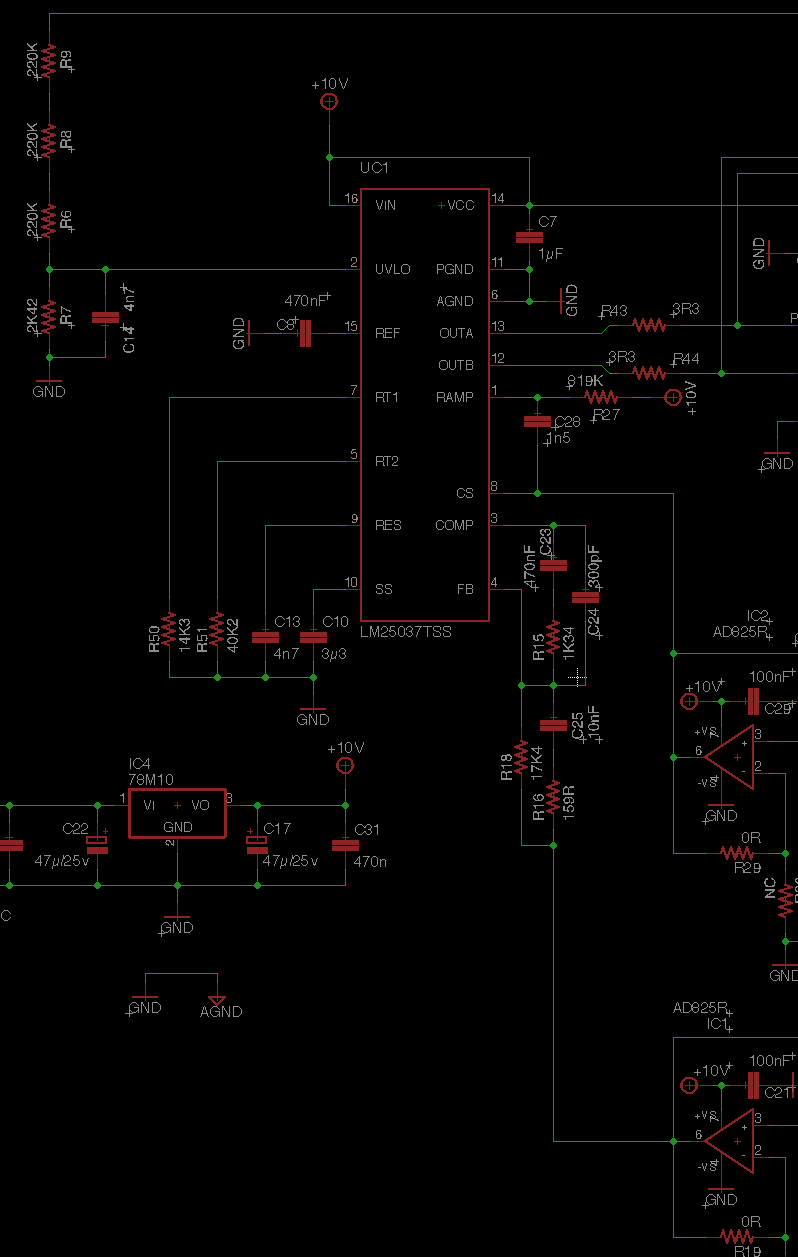

I designed a Full-Bridge Current Mode Converter based on the LM25037 controller. (390V to 350V)

I wanted to test the functionnality of the LM25037 and to see if the PWM is working good, if the mosfet are driven...

So, the transformer is not connected. I inject a voltage into the feedback loop, so that a duty cycle can happen...

The image of the output voltage is transmitted through an opto-coupler and then a PID controller is directly implemented beetween between the transistor of the opto-coupler and the FB / COMP pin of the LM25037.

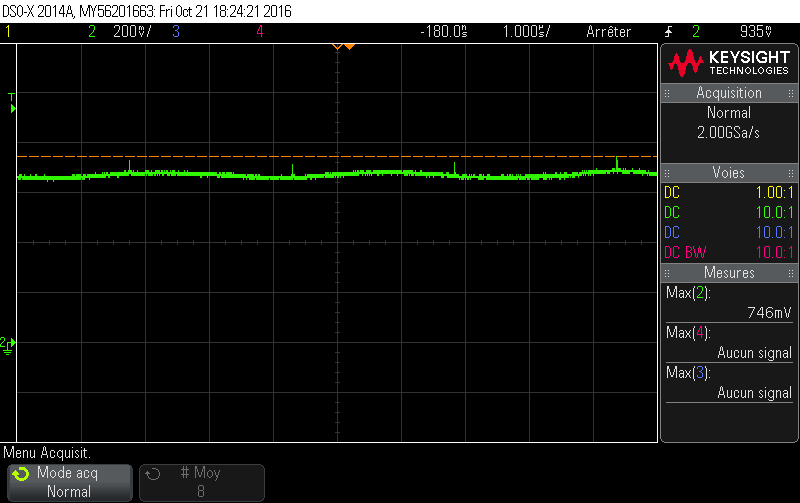

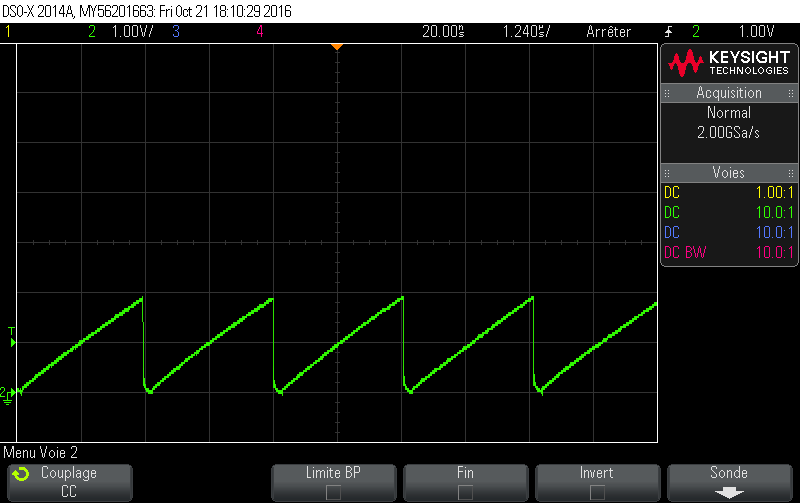

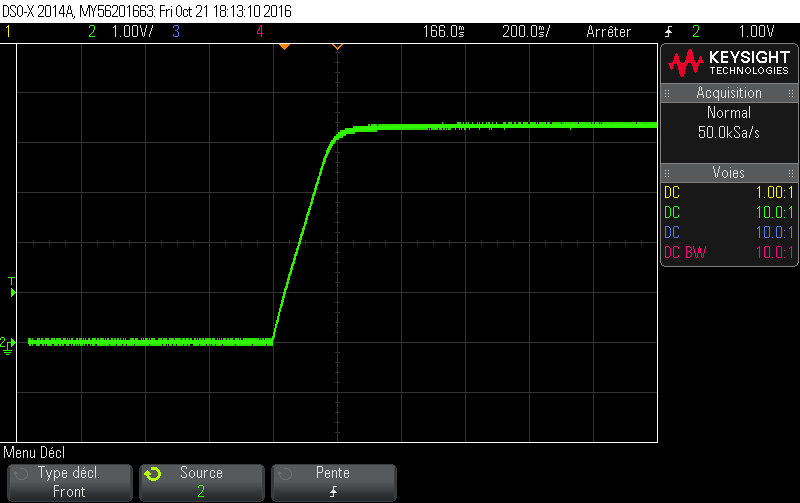

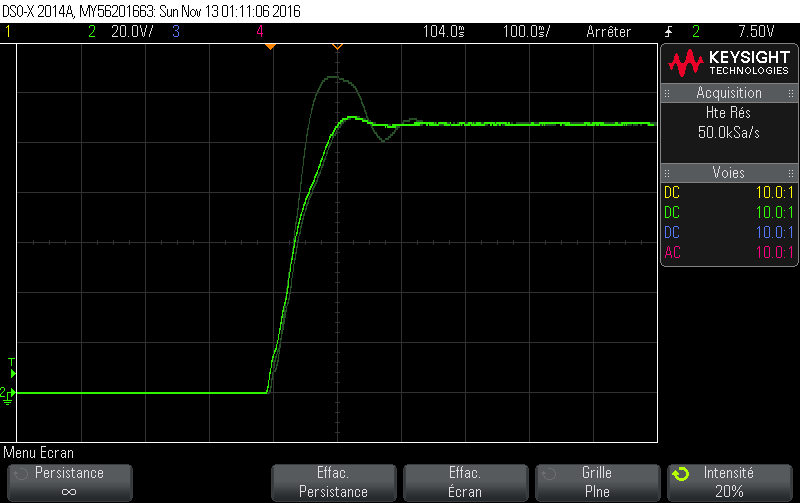

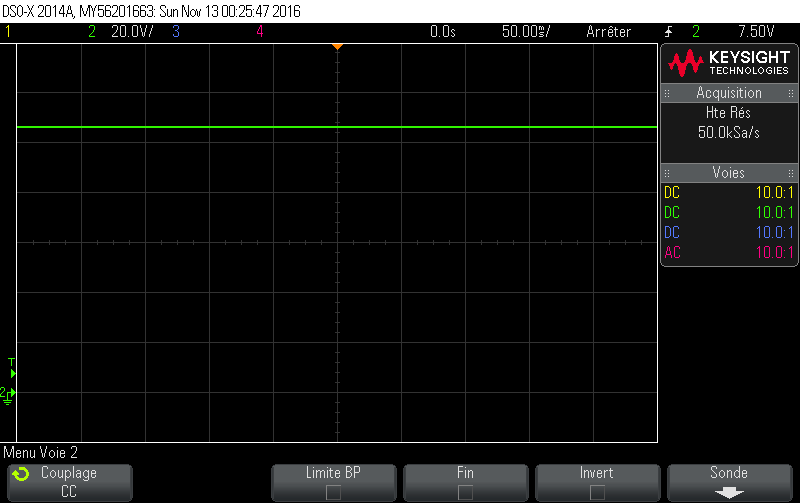

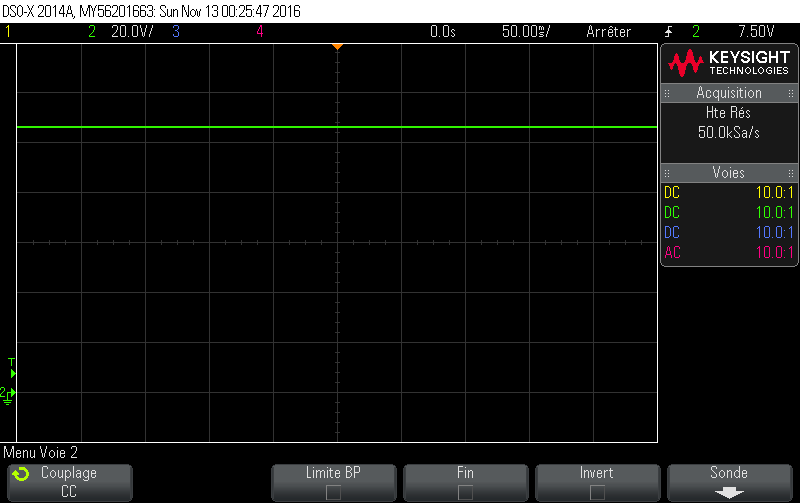

Then, I switch on the input voltage (390 Vdc). LM25037 is supplied with 10V on pin VCC and VIN.... The UVLO is OK. The Soft-Start is also OK : rises to around 5V. But I can't see any ramp signal on the RAMP pin !! It looks like the oscillator of the LM25037 does not operate...

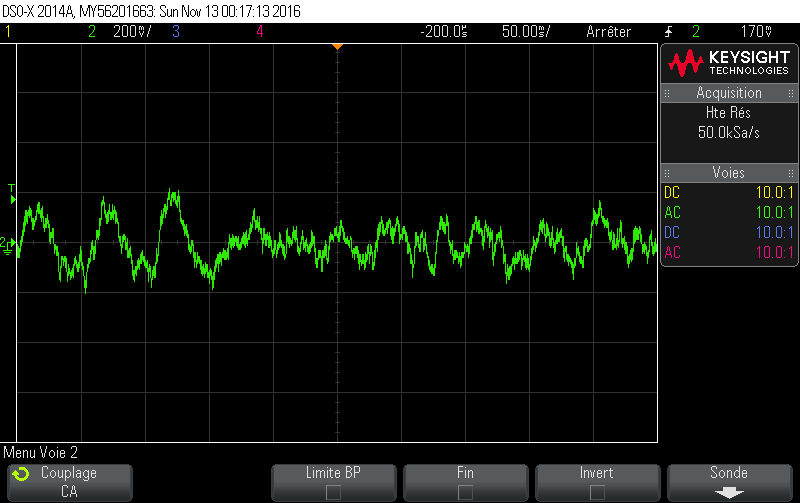

The values for RT1 is 14k7 and for RT2 is 20k (around 400 kHz clock and 200 nsec dead-time to limit the duty cycle to 88% roughly...). A voltage appears on these resistors too....

So, what's going on and why the LM25037 does not oscillate ?

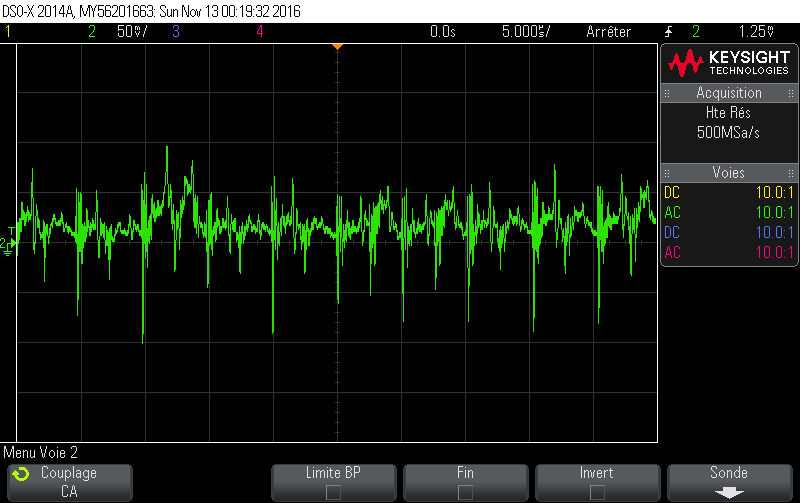

By the way, the current sensing is done with a shunt, and then a 2nd order Sallen-Key activ Filter. So, the CS pin is directly connected to the output of a OpAmp.... and then connected to RAMP through a capactor to get the slope compensation. RAMP is connected on 10V through a resistor....

Could you please help me ?

Thanks a lot,

Cheers,

Julien.