I am working on a dual switch flybck converter using UC3845.

To drive two MOSFETs, a driving transformer is used. The driving circuit is shown in fig.1.

The primary side is a DC blocking capacitor which is 1uF. The secondary side is driving resistor which is 15Ohms.

fig 1 driving circuit

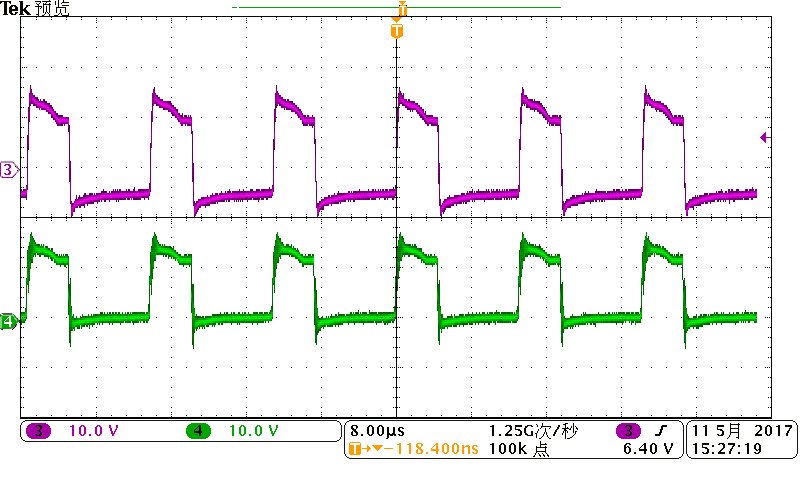

Here comes the question. The output of UC3845 pin6 is shown in channel 4 in fig.2, which is a little weird. Channel 3 is voltage across GS of MOSFET.

When the switch is on ,the voitage is not as constant as supply voltage about 14V. There is a descending ramp.

I cannot figure out why...It looks like something wrong with the IC UC3845. However if I take the DC blocking cap. The output of pin 6 is OK.

fig.2