Other Parts Discussed in Thread: TIDA-00778

Hello,

Considering to change FAN73901 to UCC27714D but like to have some better idea of the HO/LO output drive current relative to temperature range. Datasheet makes huge effort to show numerous propagation delay plots versus temperature but not 1 graph plot of HO/LO output drive current.

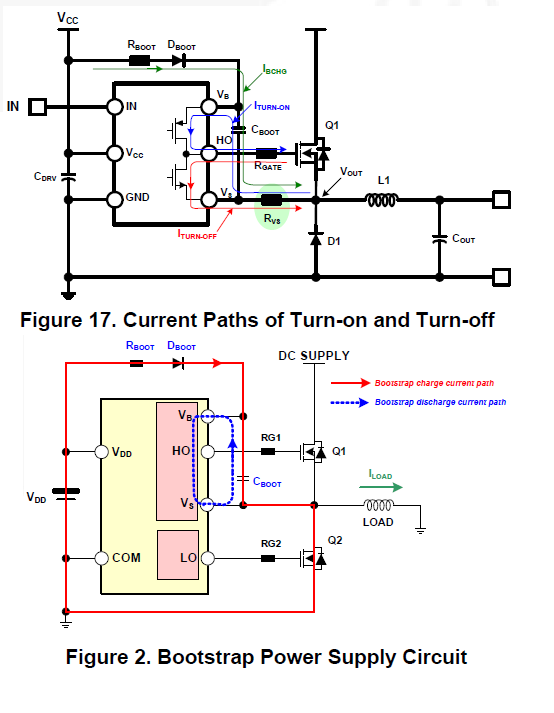

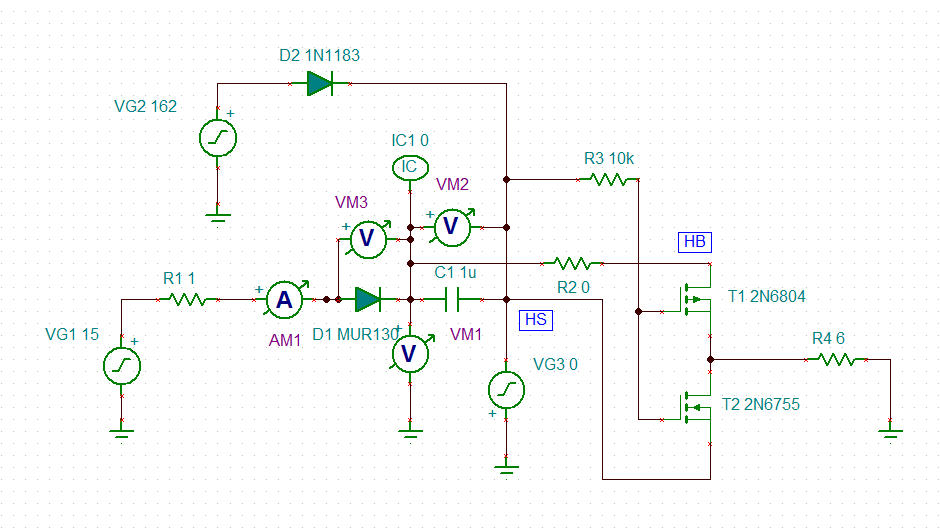

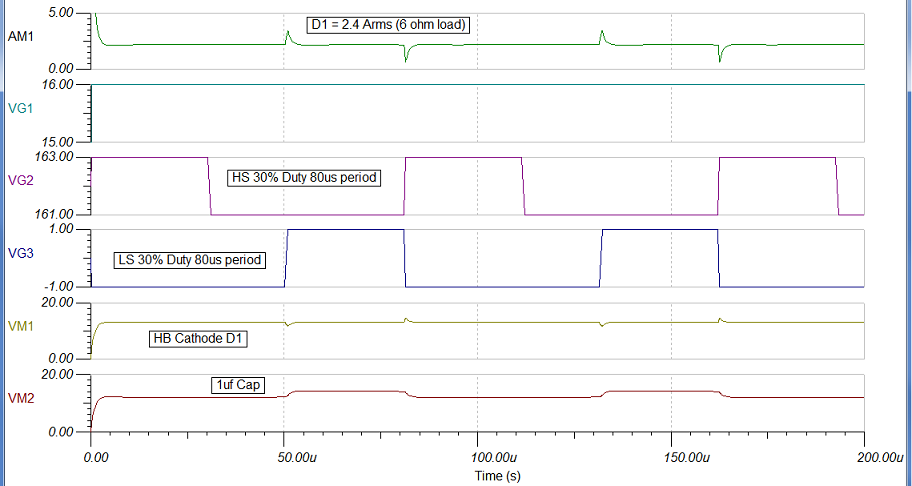

Please elaborate what is HO/LO 250ma DC versus 4 amp peak and how that is achieved when HB/HS charge pump often has 1 amp fast Dboot diode, 1uf capacitor? Most 1 amp ultrafast diodes are tested for single 30amp 1/2 sine pulse but may have issues at 10Khz, who would know being 60hz is often used 1/2 sine testing. Would it not be better to use 2amp rated diode with a 100amp peak to achieve the HB/HS 4 amp peak after each pre-charge cycle without the cathode of Dboot clipping each current peak?

According to other engineers have explained the charge pump remains active in each PWM cycle in order for HO gate region to achieve Miller plateau in QGD in the HB/HS voltage offset far above COM. Any thoughts how 10kHz to 100Khz PWM signal might effect the charge pump Dboot ability and gate driver HS/HB to maintain 4amps peak @-40*C to120*C?