Other Parts Discussed in Thread: UCC2897A, PMP20742, UCC27511

Hi Guys,

I do not have too much background of DC/DC converter design.

I just found the PMP3162 could meet our reqirement through google searching.

All the circuits parameters are same as reference design of PMP3162.

Excpt 2 parameters chage as below (out DC/DC output has change to be 12V and around 5A):

1, T1 (PA4141NL) has changed to be PA0273NL, as below:

2, L1 has changed from PG1083.682NL to PG0871.682NL (Similar Inductor value just different in Irat);

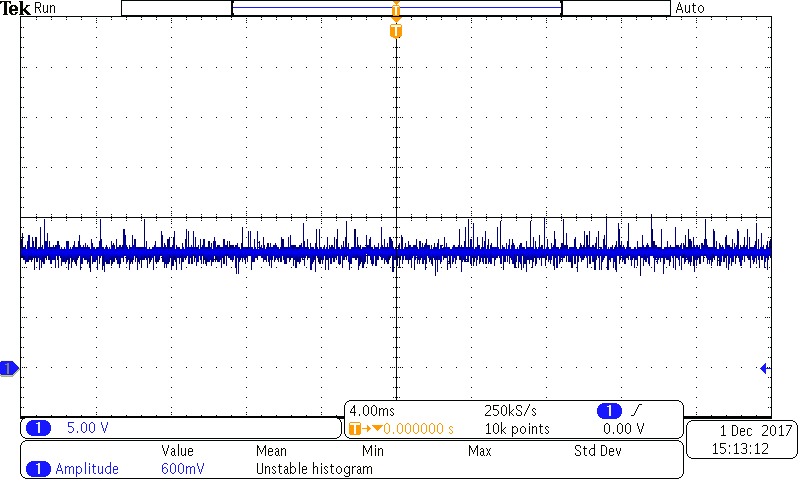

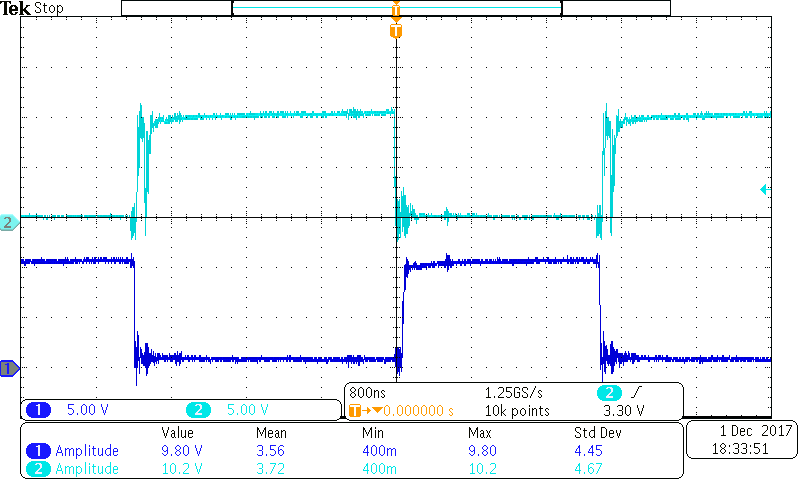

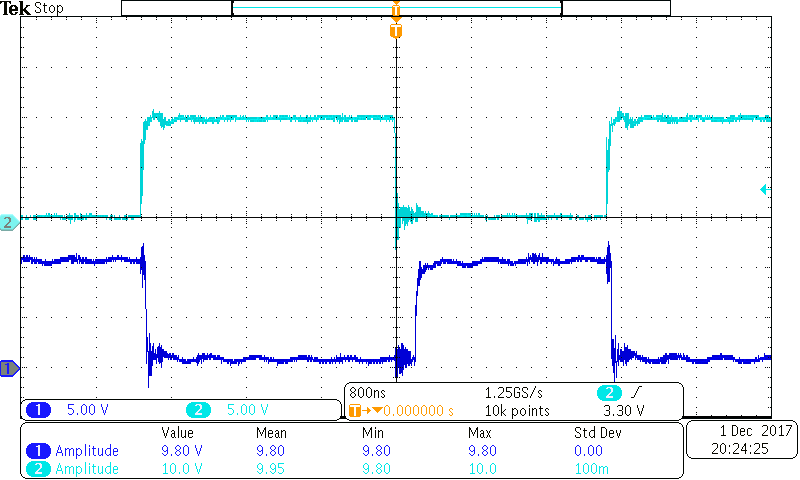

We found there has no output (Voltage of Vout kept 0) after we powered on the modified circuits, looks like the UCC2897A does not active yet.

So, anybody can offer me simple guide about how to debugging this circuits?

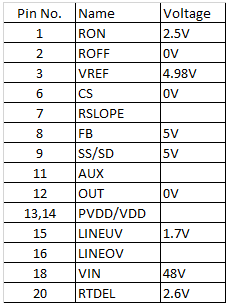

Looks like I can start to adjust the Resistor on Ron, Roff, RTDEL, RSLOPE, LINEUV, and LINEOV, or the resistor connected with opto-coupler, right?

Thank you for your reply!